您好,

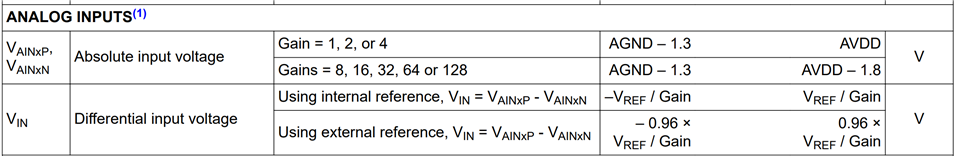

我使用的是外部参考, 根据数据表 (第7页) ,VREF乘以0.96。

是否有任何信息说明(0.96)在不同芯片和温度范围内的一致性。 还是应该为每个单元校准。

谢谢,此致。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好Afzaal:

假设您在谈论差分输入电压,那么您似乎误解了该规范。

这是为了解释差分电压的输入限制。 通过内部参考,差动电压可以利用整个满刻度范围, 而通过外部参考,您可以说您有该满刻度范围的4 % 限制。 对于需要上下文的任何其他读者,我们回顾全刻度范围(FSR)可表示为FSR = m * Vref / gain,其中m =因子,由输入类型确定(例如真差,puesdo差分,单端等)。 更多信息见本帖 :https://e2e.ti.com/blogs_/archives/b/precisionhub/posts/it-s-in-the-math-how-to-convert-adc-code-to-a-voltage-part-1

SPEC表示在使用外部参考时超出规格时导致非线性输入行为的损失。 因此,我认为询问有关校准或温度或规格范围变化的问题是没有意义的。 我建议将此视为输入的限制,即在使用外部参考时,您只能获得FSR的96 % 的线性行为。 这是否合理? 相反,如果用户能够处理动态范围内因使用外部参考而出现的骤降,此规范通常会向用户发出信号。

最佳,

-Cole

您好Afzaal:

我将与团队一起检查内部测试信号的2/15比率。

至于测试信号,我会改变我的想法,使REFIN引脚的电压与调制器所用的VREF电压有差异(即使只是数字刻度)。 由于您在REFIN引脚处使用1.25V,VREF = 1.2V。 换言之,它将是2/15*VREF或2/15*VRFIN*REFIN 0.96。 鉴于VREF用于差分电压规格,我知道这是如何令人困惑的,并且我已将该反馈传递给团队。

此外,1.2V和VREF在数据表中多次提及,您应该假定它们指的是VREF电压,而不是REFIN引脚电压。 希望这会有所帮助。

最佳,

-Cole

您好,

我提出这个问题是因为我在使用内部/外部参考时获得不同的读数。

测试信号的平均ADC读数。

内部参考资料: 106.8857万

外部参考电压(1.249V): 112.5024万

我的理解是,由于 这两种情况下的VREF都是1.2V,它们应该非常接近,而不是5 % 关闭。 所以我(不正确)猜2/15是在分割REFIN。 可能是配置错误。 我将很快进行更彻底的测试。

谢谢。

您好,

我仔细检查了所有东西。

时钟为8.3M,ADC在1024 OSR /4096 SPS下采样。

增益始终为0。

CHX_CFG最初设置为0x1以获得偏移量。

然后将其写入 CHX_ocal寄存器。

然后,CHX_CFG为0x2 ,我们 计算 4096个样本的平均值。

根据参考设置,我仍获得不同的读数。

我应该补充一点,偏移也是5 % Off。

内部参考资料:1286

外部参考资料:1354

您好Afzaal:

抽象地说,我从团队那里学到了一些知识,测试信号有两个组成部分:提供测试DAC和相应设置反馈的"反馈"。 对于温度和硅加工的变化,"反馈"可忽略不计,因为它是衡量比率的指标,因为没有更好的术语。 从1 % 设计角度来看,测试DAC不应超过+/-DAC (对于温度和过程),

在实际系统中是否有切换外部和内部的实际理由? 或者这是一项验证工作吗?

假设内部和外部是输出代码,我会说它有点偏。 您的流程看起来是正确的。 让我在EVM上完成相同的过程,看看是否可以重现它。 编辑:我手边没有干净的外部引用。 使用手头的台式设备会导致错误过多

最佳,

-Cole

编辑:已删除支持数据声明,设计团队的陈述仍然有效。