大家好,

我们希望就下面的客户咨询寻求您的帮助。

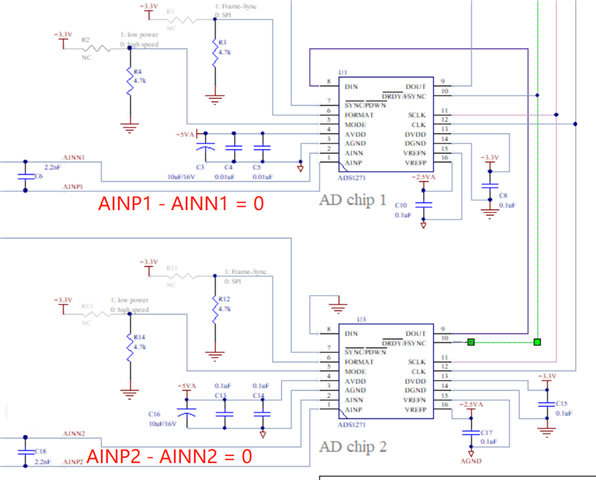

我们使用了两个ADS1271,它们由Daisy Chain提供,如下所示:

当输入为0时,我们尝试读取ADS1271,但我们通过SPI接口获得了FFF3CF 0万,如下所示:

请帮助我们检查如何从SPI接口获取有效数据。

此致,

达尼洛

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好,Danilo,

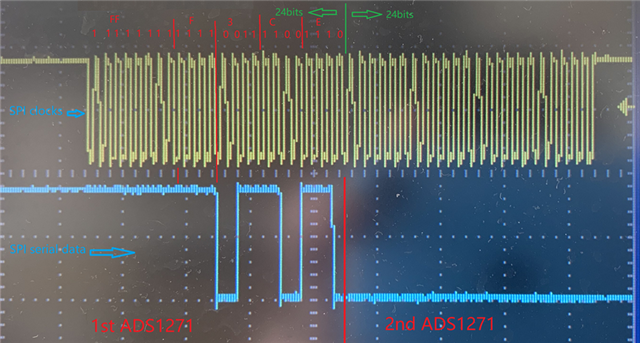

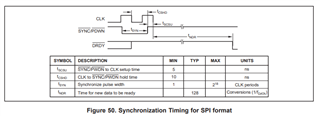

在菊花链中使用ADS1271时,ADC必须相互同步。 请让客户验证在电源稳定后,/sync针脚是否至少在1 CLK时间内断言为低电平。 为了使输出同步到相同的时钟边缘,图50中的详细定时要求是必要的。 如果不满足这些要求,只要/sync引脚在至少1个CLK周期内保持低电平,设备将在1个CLK周期内同步到。

另外,您不想将/DRDY引脚连接到多个ADC上。 在SPI模式中,这些是输出,如果一个为高电流,另一个为低电流,则可能导致过大电流。 使用菊花链时,只需要监视单个/DRDY引脚,因为所有ADC的/DRDY引脚将在部件同步后同步。

另外,请询问客户使用的CLK频率和SCLK频率。 通常,这些值相等,最多支持菊花链中的20个设备,但如果SCLK小于CLK,则会减少菊花链中支持的最大设备数量。

此致,

Keith Nicholas

精密ADC应用

您好,Keith:

感谢您调查此查询。 以下是我们客户的回应,

在我们的设计中,两个ADC1271彼此同步。 CLK频率为3.2768万Hz,SCLK频率为12MB/S 我们确信,在电源稳定后,/sync引脚至少在1个CLK时间段内处于低电平状态。

我们检查硬件并监控单个/DRDY引脚。 我们现在可以读取所有两个ADS1271,因此我们可以读取几次,而输入都是2kHz/1Vp-p,并获得这些数据:

FF B5 26 FF be 88

FF D1 C6 FF A4 91

FF C8 A5 FF B0 69

FF CA BC FF B7 D9

FF D8 12 FF B5 CC

FF C0 B8 FF BB 77

FF D2 C8 FF A2 03

FF C4 5A FF C1 A8

FF B4 C8 FF A3 1A

FF C9 D7 FF 9E 53.

FF D4 53 FF AC B3

FF C6 9E FF B5 6A

FF B8 B5 FF C2 D5

FF CE 57 FF CA 9C

。。

这些数据看起来无效,我们不了解发生了什么,请帮助我们。

此致,

达尼洛

您好,Keith:

我们的客户认为,

我们将CLK频率提高到328kHz,同时输入全部为2kHz/1Vp-p,然后我们得到了一些数据,例如:

FF C5 07 FF B3 DF

FF C9 1F FF AF 20

FF C9 9C FF B1 68

FF C1 4E FF B0 83

FF C9 96 FF B1 AE

FF C0 47 FF B4 CA

FF D1 F0 FF B5 A8

FF CC 11 FF B6 04

FF C3 8B FF B2 08

FF BF 95 FF AB F6

FF C4 8E FF B2 22.

FF C7 47 FF B0 26.

FF C1 F0 FF B3 76

FF CA 2D FF B7 44.

FF C4 BB FF A9 01

FF CC 5A FF B4 E9

FF C7 90 FF B4 D0

FF D0 B3 FF AD 11.

FF C6 6D FF B4 06

FF D3 F8 FF B5 DB

它们看起来无效。

此致,

达尼洛

您好,Keith:

我刚刚收到客户的回复。

当"AINP-AINN = 0"时,我们有两次采样。

我们第一次获得这些数据:

FF C7 D3 FF B3 4C

FF C7 EC FF B5 E6

FF C8 44 FF B4 62.

FF B4 E1 FF A1 23.

FF E8 7E FF D5 E5

FF be 31 FF AA A8

FF C6 F6 F6 FF B3 8F

FF CD 78 FF B9 C1

FF C4 34 FF B0 05

FF CC E4 FF BA 43.

FF C1 80 FF B0 80

FF CE 4B FF B9 92

FF C3 F1 FF B1 46

FF CB F1 FF B8 1B

FF BB 9B FF A7 43.

FF EA 65 FF D3 F4

FF BC 89 FF A7 FA

FF CA 7B FF B5 57.

FF CD 79 FF B7 29.

FF C4 9D FF B1 E7

在另一个时候,我们获得了这些数据:

00 13 BD FF FF 70

FF D0 6C FF BC 66

FF C1 C5 FF AE 9F

FF CF 51 FF BB 27.

FF be 01 FF AB 80

FF C1 C3 FF AC EA

FF E5 D3 FF D2 3D

FF BA B4 FF A5 E5

FF CB A0 FF B8 A5

FF C9 3C FF B4 D7

FF C5 3A FF B1 F3

FF CD B9 FF B9 31.

FF C4 5D FF AF 8D

FF D0 D2 FF BD 63.

FF be 9C FF AA 1E

FF D6 9F FF C2 58.

FF B9 41 FF A7 20.

FF DA 9B FF C7 F9

FF A7 96 FF 93 FF

我们得到了一张样品图片,但我们无法加载它。 它看起来像以前加载的示例图片。

此致,

达尼洛

你好,Danilo,

理想的转换读数应为0V,AINP-AINN=0V。 数据不是很远,但噪音很大,大约8mVpp。

| 十六进制 | 十进制 | 毫伏 | 十六进制 | 十进制 | 毫伏 |

| 0013BD | 5053. | 1.506 | FFFF70 | -144. | -0.043 |

| FD06C | -1.218万 | -3.630 | FFBC66 | -1.7306万 | -5.158 |

| FFC1C5 | -1.5931万 | -4.748 | FFAE9F | -2.0833万 | -6.209 |

| FFCF51. | -1.2463万 | -3.714 | FFBB27 | -1.7625万 | -5.253 |

| FFBE01 | -1.6895万 | -5.035 | FFB80 | -2.1632万. | -6.447 |

| FFC1C3 | -1.5933万 | -4.748 | FFACEA | -2.127万 | -6.339 |

| FFE5D3 | -6701 | -1.997 | FD23D | -1.1715万 | -3.491 |

| FFBAB4. | -1.774万 | -5.287 | FFA5E5 | -2.3067万 | -6.875 |

| FFCBA0 | -1.3408万 | -3.996 | FFB8A5 | -1.8267万 | -5.444 |

| FFC93C | -1.402万 | -4.178 | FFB4D7 | -1.9241万. | -5.734 |

| FFC53A | -1.5046万. | -4.484 | FFB1F3 | -1.9981万 | -5.955 |

| FFCDB9. | -1.2871万 | -3.836 | FFB931 | -1.8127万 | -5.402 |

| FFC45D | -1.5267万 | -4.550 | FFAF8D | -2.0595万 | -6.138 |

| FD0D2 | -1.2078万 | -3.600 | FFBD63 | -1.7053万 | -5.082 |

| FFBE9C | -1.674万 | -4.989 | FFAA 1e | -2.1986万年 | -6.552 |

| FD69F | -1.0593万 | -3.157 | FFC258 | -1.5784万 | -4.704 |

| FFB941 | -1.8111万 | -5.397 | FFA720 | -2.2752万 | -6.781 |

| FFDA9B | -9573 | -2.853 | FFC7F9. | -1.4343万 | -4.275 |

| FFA796 | -2.2634万. | -6.745 | FF93FF | -2.7649万 | -8.240 |

ADC确实可以正确转换输入电压,通信也是正确的。 此时,噪音很大可能与主板布局有关,或者电源设备上可能有很多噪音。

您能否提供主板布局的图片? 客户是使用ADS1271EVM板,还是 在客户的电路板设计上测量此数据?

此致,

Keith

您好,Keith:

我刚刚收到客户的反馈。

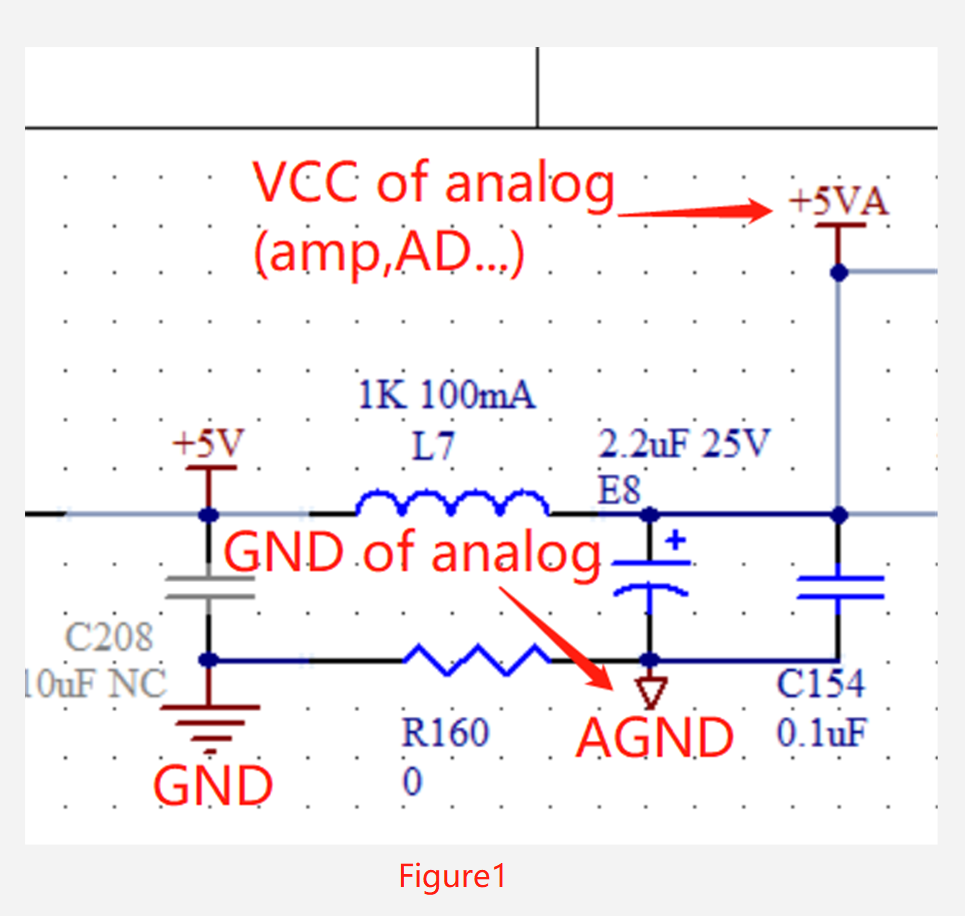

是的,这些数据是在我们的主板设计上测量的。 我们通过简单的电路获得了+5VA&AGND,如下所示:

图1.

我们的布局层如下所示:

——— 顶层

——— GND/AGND层(AGND是模拟GND,它来自GND。)

——— VCC/+5V/+5VA层(+5VA是模拟VCC,它来自+5V。 +5V (5.3V)由DCDC产生。)

——— 底层

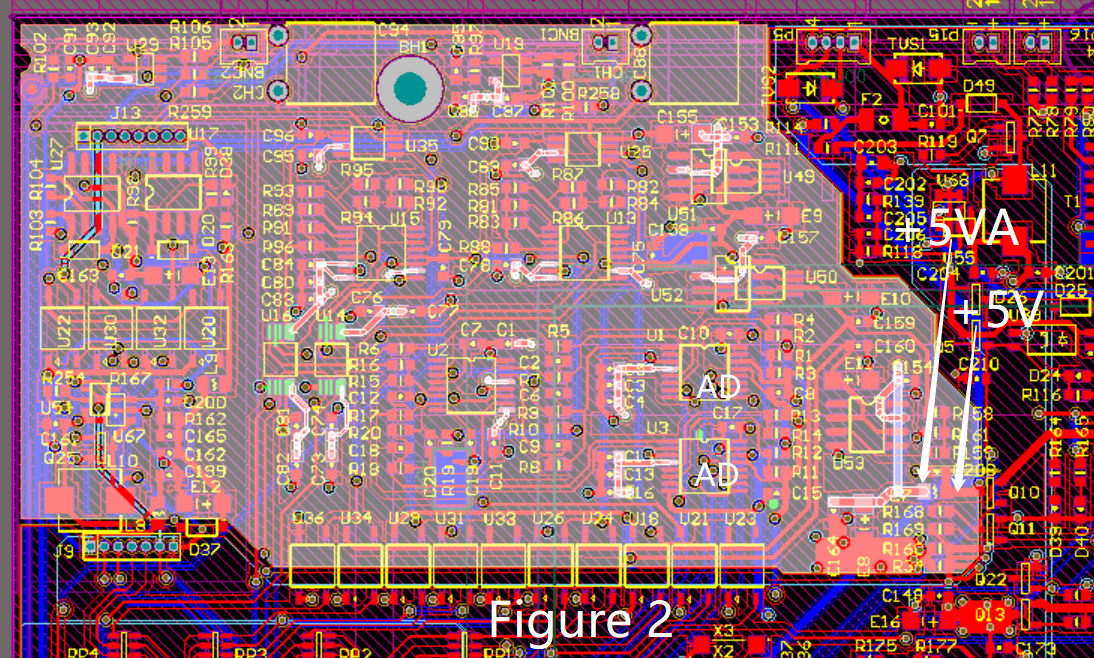

+5VA的布局如下所示:

图2.

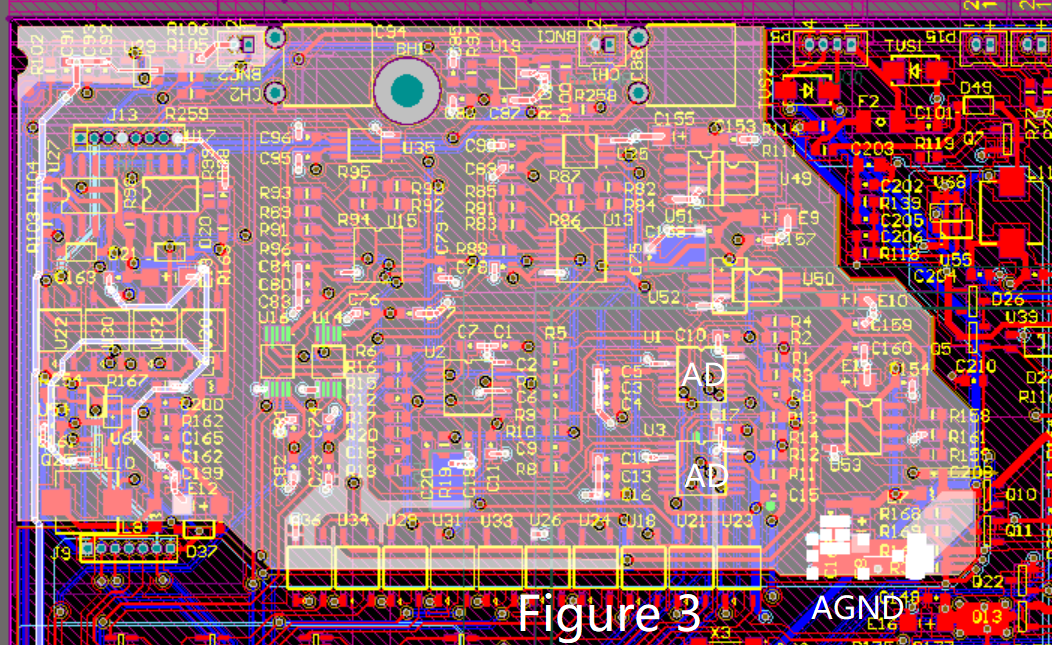

AGND的布局如下所示:

图3.

可能噪音很大。 我们希望收到您关于设计和布局的建议。

此致,

达尼洛

你好,Danilo,

ADC输入与滤波器网络之间的距离较大。 这可能会产生噪音,尤其是在输入附近有数字轨迹时。 通常,我们希望差分输入电容器尽可能靠近IC引脚。 我假设该主板使用一个内部接地平面,正位于ADC焊接到主板的顶层下方。 否则,应使用接地平面。

此外,每个参考引脚上的电容器仅为0.1uF。 我建议将其至少提高到1uF。

如果数字和模拟接地针脚之间存在大量噪音,这也可能会损坏读数,从而导致更高的噪音。 我们建议将IC的接地直接连接到IC套件旁边。 在上述布局中,接地通过R160连接在板的右下角。 有关详细信息,请查看精密ADC的推荐接地布局。

此外,所有数字迹线都应远离模拟迹线,包括参考输入和模拟输入。 如果这些信号是直接在彼此之下或在同一层彼此相邻,则可以将数字噪声耦合到模拟输入中。 我们通常在评估板的布局中,所有数字信号都在板的右侧,所有模拟信号都在板的左侧,以确保数字信号和模拟信号之间没有耦合。

如果客户可以提供显示输入放大器和参考电路的附加示意图,我可以再看看是否有其他建议。

此致,

Keith