主题中讨论的其他部件:ADS1278

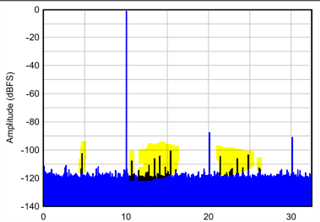

根据线程,时钟输入和SCLK输入应具有相同的时钟源,以避免ADC频谱中出现突起(我不理解 ADC频谱中的突起是什么)。

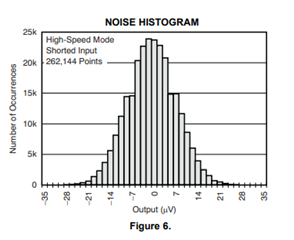

我已将FPGA连接到ADC。 FPGA的时钟输入是200MHz的振荡器。 内部PLL可以生成 13.5MHz的时钟和27MHz的时钟。 我是否可以 通过FPGA IO将13.5MHz连接到ADC SCLK引脚,将27MHz时钟连接到ADC CLK输入引脚?数据表显示应使用低抖动时钟。 通过FPGA IO的时钟信号是否为低抖动IO?

数据表显示 晶体可以使用,但我不知道如何将晶体连接到单时钟输入引脚,在大多数情况下 ,晶体 应连接到设备的2个引脚。