Other Parts Discussed in Thread: ADS7040

主题中讨论的其他器件:ADS7040

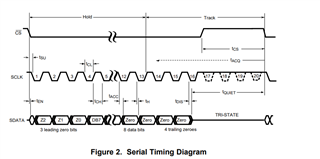

数据表指出、"如果 CS 在第10个下降沿之后、但在第16个下降沿之前变为高电平"、则中止采样、但不会解决这对下一个/CS 下降沿时序的影响。 在什么沿可识别中止、发生这种情况时器件是否立即返回跟踪模式、或者是否预计计时会继续、且在12.5个时钟后跟踪模式仍正常进入?

换而言之、如果时钟继续、/CS 下降沿之间的最短时间是否完全受中止影响?

好奇的是、这不是性能优化问题。 相反、我正在构建一些极简的逻辑来读取串行 ADC、并希望结果与尽可能多的廉价8位 ADC 兼容(其他可能的备选器件是 ADS7029和 ADS7040)。 吞吐量部分中描述的16周期1MHz 方案对我来说非常有吸引力、但是由于硬件资源极其稀缺、/CS 的确切持续时间需要仔细进行预算。 我希望16周期1MHz 帧时序保持不变、无论输出 DB7后是否立即"中止"采样。

非常好

Aaron