Other Parts Discussed in Thread: ADS131M06

我在设置 ADS131M06时似乎遇到问题。 我可以读回我设置的寄存器、但输出似乎没有差异。

我已使用示波器检查信号以检查边缘质量、并使用逻辑分析仪检查信号以确保较长的位流正确。 此外、读回寄存器为我提供的值与我写的值相同、这表明写入操作正常、这提供了信号时序和位顺序的二次检查。

我向时钟寄存器写入0x3F1E 值、结果应在时钟寄存器中

启用通道0-5

对于16256的 OSR、OSR 位设置为7;对于8.192MHz 的 CLKIN 速率、转换率设置为250SPS

PWR 位设置为2或默认的高分辨率

此外、我向模式寄存器写入0x511值、结果应在模式寄存器中

寄存器和输入 CRC 禁用

复位位位保持高电平

启用 SPI 超时

最滞后的通道控制*DRDY

*无数据就绪时,DRDY 驱动为高电平

* DRDY:在8.192MHz 时钟速率下具有4个 CLKIN 或~0.5uS 的低电平有效脉冲。

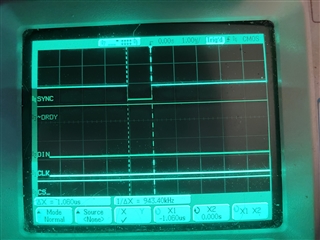

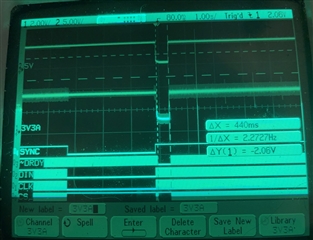

不过,我看到*DRDY 速率为4kHz+,信号通常较低,如图所示

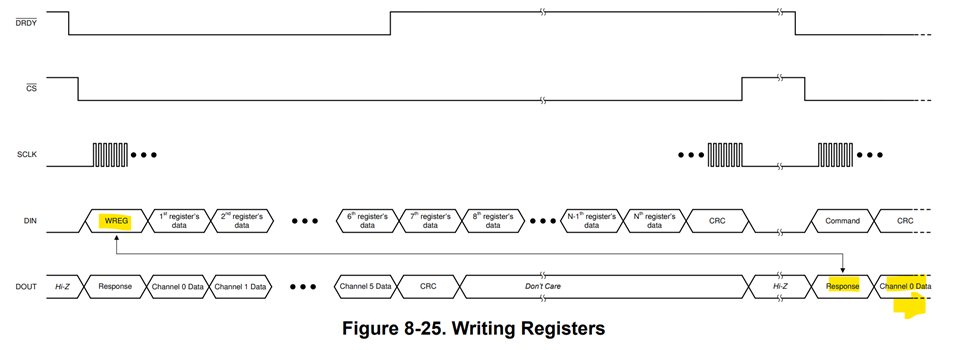

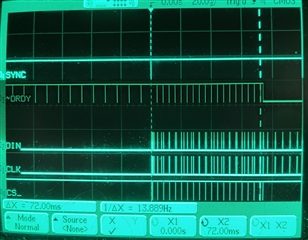

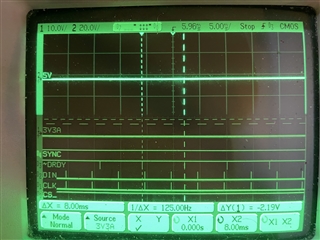

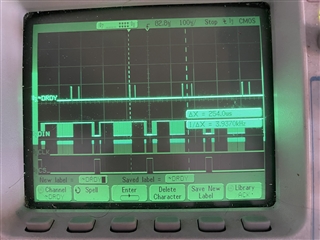

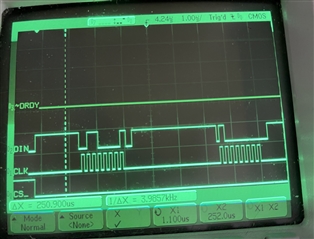

下一个屏幕显示时钟寄存器的写入序列

两张图片显示了该写入的详细信息

首先执行命令

然后是寄存器值

我具有用于写入模式寄存器的相同序列。 不过、我认为它不会增加太多信息。

我确定数据表中的内容缺失或误解、但此时我不知道是什么。 在~给定这些设置(由于内部缓冲、最高可达500)的情况下、我本来希望从* DRDY 线路获得窄低脉冲、但我得到的是多数低线路和4kHz 频率。 这些设置似乎不会影响行为。 对我所遗漏的内容有什么想法吗?

Robert