Other Parts Discussed in Thread: CDCE62005, DAC3283

主题中讨论的其他器件:CDCE62005、

我正在使用 DAC 3283使用 Artix 7 FPGA 执行一个项目、同时使用 CDCE62005生成所需的数据时钟和 DAC 时钟并为 DAC3283提供输入。

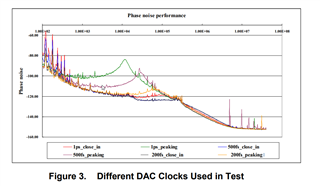

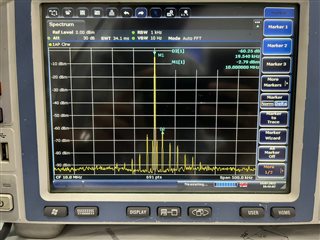

DAC_CLK 采样频率为400MSPS。 在 Xilinx Vivado 18.2工具中使用 DDS 编译器为 DAC3283提供的数字输入为10MHz。 我们得到的模拟输出

使用频谱分析仪观察到的10MHz、3.22dBm。但通过在10Hz 左右设置1Kz 分辨率带宽(RSW)和 vedio 带宽(VBW)、以增大杂散电平、其跨度范围为

500kHz,我们得到57 dBC。 在数据表中,显示10MHz 杂散电平将大约为80dbc 至85dbc。 现在、对于我生成的10MHz、需要大于75的杂散电平。

以及如何实现它?K

通过更好的解决方案进行低延迟的回复。

提前感谢