主题中讨论的其他器件: TPS7A8300

你(们)好

我们在运行 DAC39J84的一些硬件上看到了一些奇怪的行为。

问题

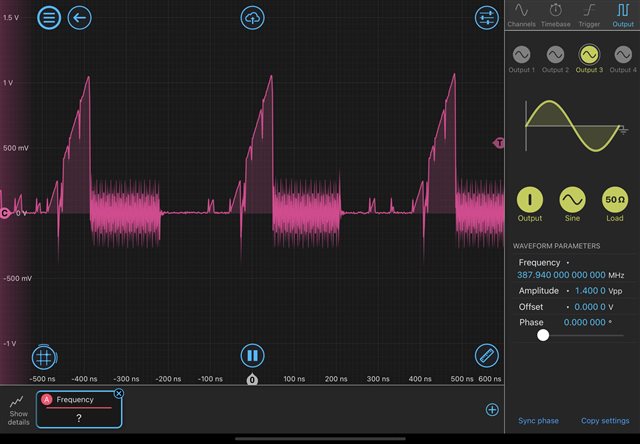

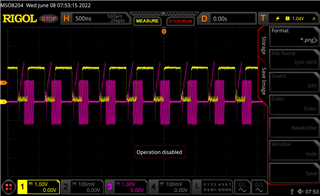

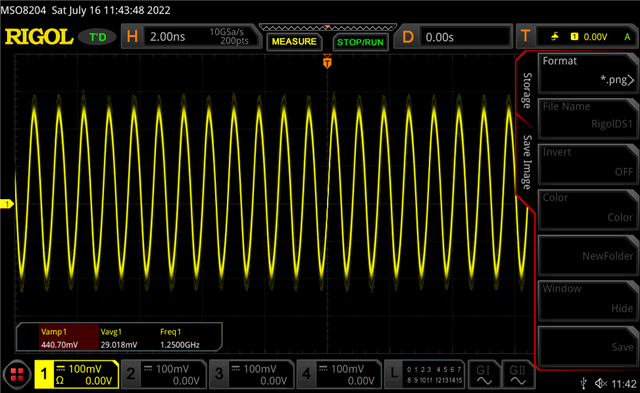

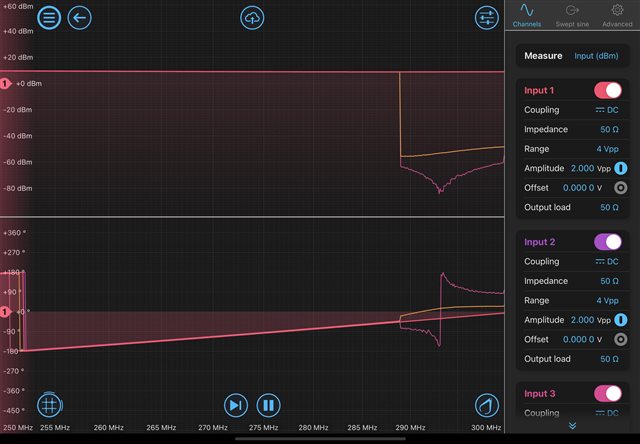

我们在 FPGA 上生成从直流到300MHz 的一系列正弦波、DAC39J84的输出电平大约为满量程的90%。 这通过 JESD204b 传输到 DAC、我们将运行2倍的内插速率以生成2.5GSPS 输出样本。 在大多数已经构建的单元上、我们能够在90%满量程时可靠地生成直流至300MHz 的正弦波、而不会出现任何问题。 但是、在多个器件上、我们观察到信号在特定频率下下降到~0 *(请参阅底部的编辑)、这在故障器件之间有所不同(已将压降频率视为230-295MHz)。 在频率扫描中、这显示为下图。

CHA/CHB 和 CHC/CHD 中同时出现信号压降、并且行为不同。 例如、在上图中、只有 CHC/D 会丢失信号。 更令人困惑的是、信号压降频率随振幅的函数而变化:在较低的振幅下、该截止频率被推高。

最后、这种行为并不总是存在的:器件上电可使问题消失、并且所有通道上都能正确生成正弦波。 它似乎与温度无关、并且在下电上电时是否存在问题似乎是随机的。 在问题出现时对 DAC 和时钟进行重新编程无法解决问题-只有重启才能解决问题。

我们的 DAC 设置为:

- 8个速率为12.5Gbps 的 JESD204b 通道

- 增益和偏移控制被启用、标称值分别为1024和0

- 禁用反向正弦滤波器

- 功率放大器保护被禁用

- NCO 和混频器模块被禁用

- 小部分和大部分延迟块被禁用

- 启用抖动

调试

我已完成以下测试:

| 测试 | 结论 |

| 将输入设置为常数0、并打开 NCO 以生成正弦波。 将所有通道上的正弦波振幅和频率设置为高于截止频率、我可以确认信号是否存在。 | 似乎不是 NCO 下游的问题 |

| 禁用 NCO 后、以镂空频率生成信号、然后降低输入振幅、直到正弦波再次出现。 然后在 DAC39J84中使用数字增益将信号振幅提高到原始电平。 信号不会因此而被切断 | 问题不是增益块的下游 |

| 监控发送端和接收端的 JESD 链路是否存在错误、同时关闭所有掩码。 无法观察到任何 JESD 链路或时钟错误 | JESD 链路中似乎没有出现问题 |

|

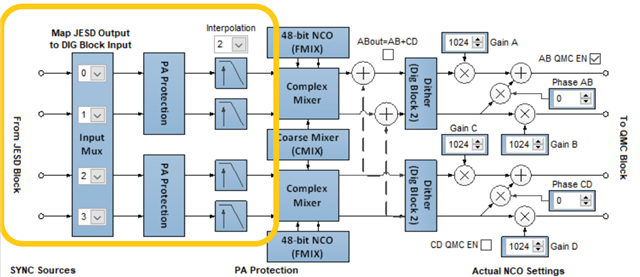

在镂空频率(290MHz/90% FS 振幅)下生成相同的波形、并通过 JESD 进行传输。 在默认配置下、两个通道正常工作、两个通道不工作(如上图所示)。 使用"ap JESD Output to dig Input"块:将"gon"通道 JESD 信号连接到"Bad"通道数字输出。 错误仍然存在 |

问题似乎出现在 JESD 输出到 DIG 输入多路复用器处或之后 |

|

使用"MAP DIG 输出到 DAC 输入"块将"良好"数据连接到"不良"通道、信号看起来良好。 将"坏"数据连接到"正常"通道、信号看起来很差。 表示 DAC 输出电路正在工作、问题似乎在 DAC 输出之前出现。 |

DAC 输出正在工作 |

当前状态

我的电流猜测是在数字数据中的 NCO/混频器块之前出现了一个问题、但我看不到发送到 DAC 的 JESD 数据中有任何问题、因此我认为它必须发生在 DAC 中的下面的圆框内。 我不明白为什么:

- 我们生产的大多数电路板都不存在此问题

- 重启电源时问题有时会消失

如果部件出现故障、似乎只是偶然发现了这一点、这对我们来说是一个问题。

感谢您的任何帮助。

编辑

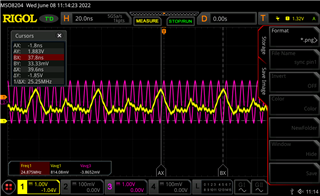

有时、信号不会降至零、而是显示为:

发生这种情况时、我无法看到任何警报或 JESD 链路错误。