你(们)好

我想知道、对于 ADC 时钟为74Mhz 的 ADS5294、160MHz 至180Mhz 的输入模拟频率、SNR 是多少。

此致,

Ashish

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Ashish、您好!

感谢您给我们写信。

根据您的规格、您的信号位于第三奈奎斯特频带。

与第一奈奎斯特频带相比、由于内部 ADC 级的带宽不匹配、您会看到 SNR 下降。

我没有74 MSPS 的数据、但在数据表中、我们共享了80 MSPS 采样率下输入频率下的 SNR 数据。 我认为棒球场编号应该保持在接近这一点的位置。

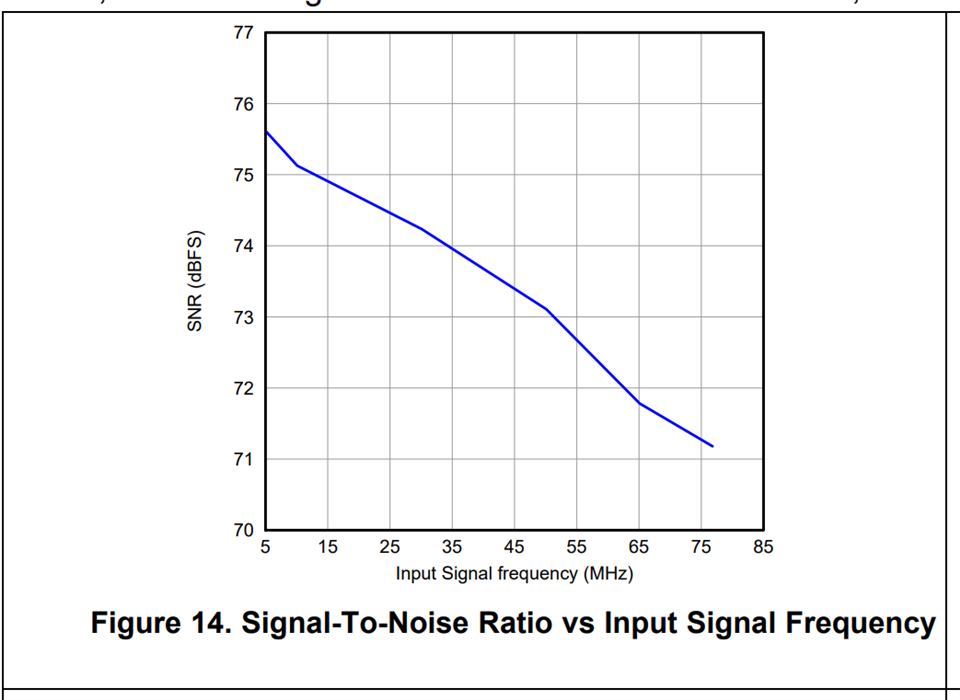

从数据表中的图14可以推断160MHz 至180MHz 的预期 SNR、分别约为66.2dBFS 至64.9dBFS。

谢谢、此致、

Abhishek

Ashish、您好!

对于高于80MHz 的频率、必须按比例降低输入信号的振幅、以保持增益带宽积(A.w)恒定、从而保持 SNR 性能。

但是、由于带宽不匹配、根据图14、预计 SNR 会下降。

因此、输入幅度衰减本身通过保持图14中曲线的斜率几乎恒定来处理 SNR 下降。 预计不会进一步降级。

我希望它能回答你的问题。 顺便说一下、这种性能是否可以为您所接受?

谢谢、此致、

Abhishek

您好、Abhishek、

我尝试在电路板设计中检查 ADS5494的性能,并附上了下面的原理图和 HSDC pro 输出。

e2e.ti.com/.../8637.adc_5F00_1.pdf

我通过 带通滤波器从矢量信号发生器提供74Mhz 和160MHz 模拟输入频率的 ADC 时钟。

我只能获得49dBFs 的 SNR,因此可以采取哪些措施来提高 SNR,还可以在 评估板中模拟此频率并 分享结果。

谢谢、此致、

Ashish

Ashish、您好!

我对您分享的波形进行了一些思考。

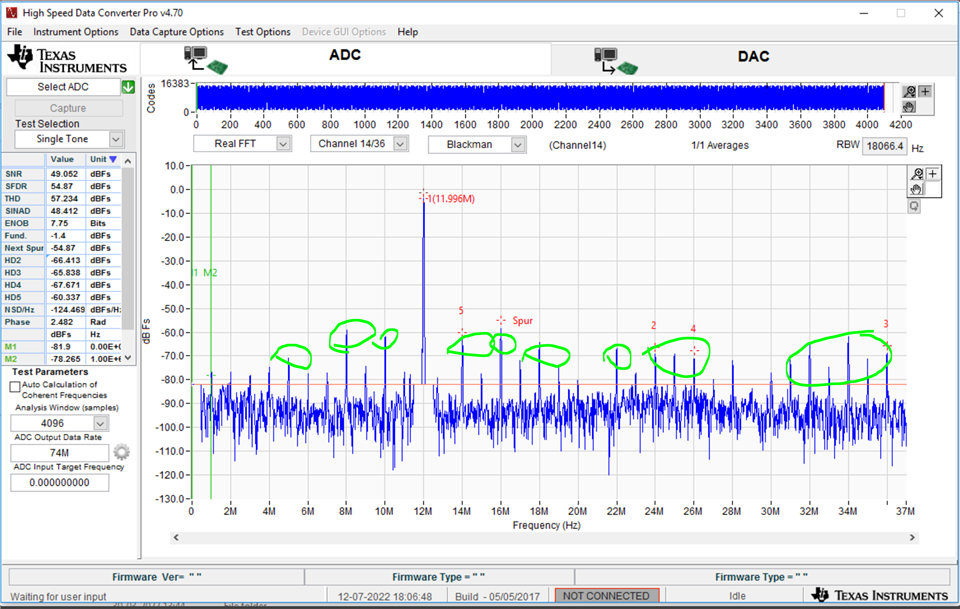

我怀疑您的 SNR 不受本底噪声的限制、而是受 FFT 中出现的杂散/谐波的限制。 我在下面的波形中也强调了这一点。

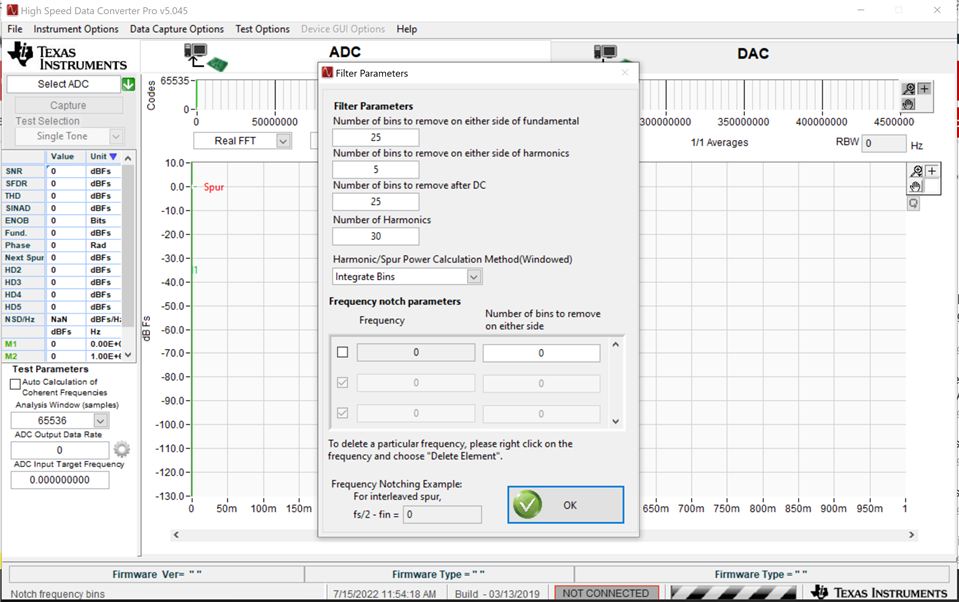

因此、为了更好地理解它、您能否在 SNR 计算中移除这些谐波后告诉我 SNR。 您可以使用测试选项中的陷波频率窗口选项、并去除大约30个谐波。 下图显示了在 HSDC Pro 中执行该操作的方法。 数据表编号通常随这些谐波的消除而提供。

接下来、我想让您了解一下您的应用。 此系统的应用是什么? 您是否在寻找更好的噪声性能、即 SNR 或 基波信号与输出中最强寄生信号( 即 SFDR)的更优强度比?

请告诉我您的意见。

谢谢、此致、

Abhishek

Ashish、您好!

很抱歉、由于个人紧急情况、我已经离开办公室了一段时间。

我回到办公室后、获取了输入频率高于80MSPS 时的器件性能数据。

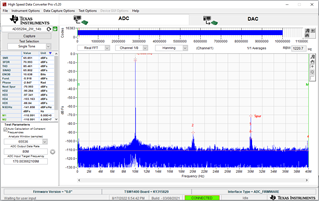

我找到了与外推波形一致的结果。

下面是在80MHz 采样率下170MHz 输入的数据。

观察到的 SNR 接近65dBFS。 我也成比例地降低了输入振幅。

我认为它在您的情况下不起作用的原因可能是您没有在信号路径中放置带通滤波器、并且由于无缓冲 ADC 而产生大量反射和采样干扰。

您能否通过引入170m 的 BP 滤波器来检查性能并分享结果。

器件用户指南还指定了如下所示的内容。

另外、请注意、我用于本实验的信号源是 SRS SG382、它具有非常好的相位噪声性能。 您的性能也可能受到您向 ADC 呈现的信号源的限制。

谢谢、此致、

Abhishek

您好、Abhishek

很高兴听到您的声音,我希望您很好。

我仍然尝试使用带通滤波器、但得到的 SNR 大约为55.8dbfs

IM 从矢量信号发生器(SMBV100A)和 AFE31000的 ADC 时钟源馈送170MHz。 我的应用需要74Mhz ADC 时钟、因此我在此时钟频率下进行测试。

我看到这两种仪器的数据表中的相位噪声都很好。

我怀疑我的 ADC 原理图,因为您提到“ 采样干扰是由非缓冲 ADC 造成的”,您能详细说明一下吗,我是否应该对原理图进行更改?

谢谢、此致

Ashish

Ashish、您好!

奇怪的是、您的本底噪声高于我在输入 BP 滤波器后看到的噪声。 我认为滤波器工作不正常、您能否分享您正在使用的带通滤波器的详细信息。

顺便说一下,如果可能,您可以在我的电子邮件 中共享您的详细联系信息:abhishek.vishwa27@ti.com。 我们可以通过电话连接、并尝试更快地解决此问题。 如果您的办公室在印度、我们可以计划将带通滤波器发送给您、您可以检查情况是否如此。

通过采样毛刺脉冲、我的意思是 ADC 的输入直接来自源、路径中没有缓冲器。 通常、对于非缓冲 ADC、采样干扰可能会出现、并且可能会反映和恶化信号特性。 通常可以通过在信号链中使用窄带通滤波器来避免这种现象。

我将您的原理图与 EVM 进行了比较、看起来是一样的。 因此、我认为您无需对原理图进行任何更改。

谢谢、此致、

Abhishek