大家好、

我的客户的器件存在问题、请参阅下面的详细信息以了解他们的问题。

TI AFE 5832-LP 电路板的内部不均匀设置存在问题。

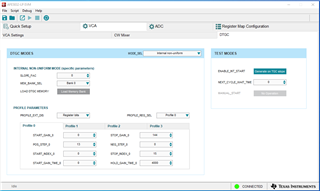

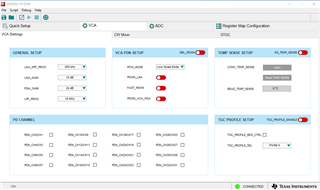

这是我设置的 DTGC 参数

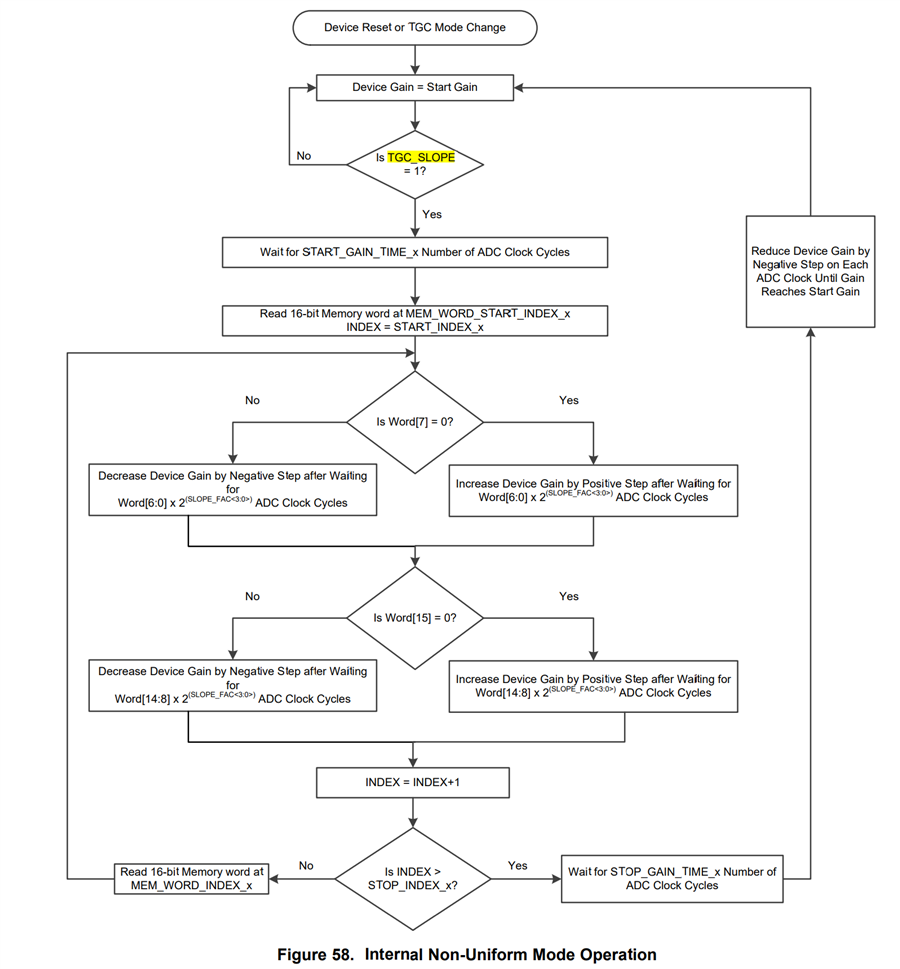

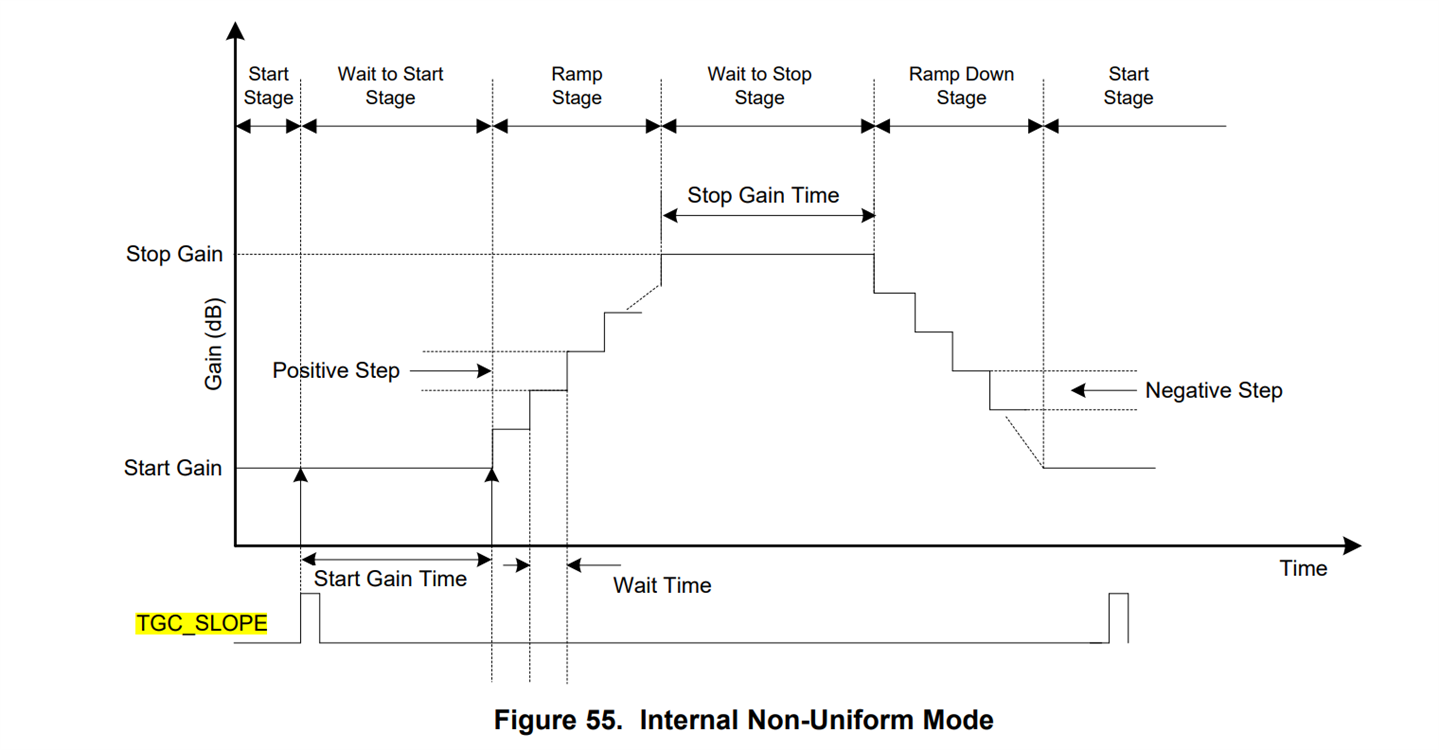

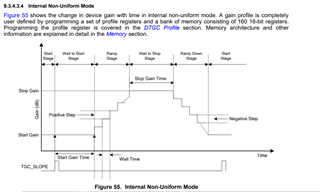

我将根据用户手册解释我使用的信号

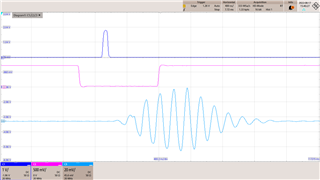

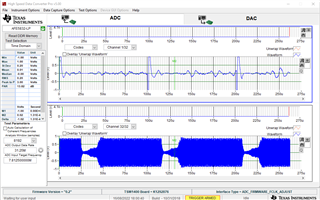

这是我使用的模式、在该模式下、TP37中使用的 TGC_SLOPE 信号是我的信号、如通道1的下一张图片所示

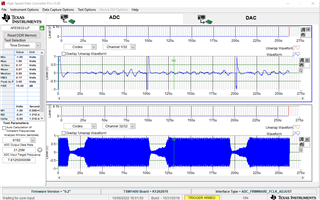

如您在通道1/32中所见、TGC_SLOPE 每100uSec 斜率累加一次、而通道32/32中的增益与该信号不同步、您还可以看到下图:

通道32/32的起始位置与通道1/32中的脉冲不同、时间为0uec 和100uSec 200uSec 等等。 我希望在 CH 1/32中的信号为高电平的点(高于1伏,正如您在 CH1/32中看到的 c=vcan 那样),增益将非常低,如果这些通道将同步, 那么、正如您在 ch32中看到的、该高电压将具有低增益、其中增益值较低

谢谢你。

此致、

5月