Other Parts Discussed in Thread: ADS42JB46

大家好、

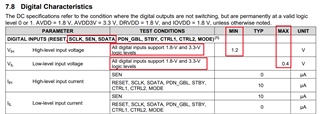

我对 SPI 控制信号的 ADS42JB46逻辑电平有疑问、

1) 1)我 看到此 AD 器件可以同时支持1.8V 和3.3V、那么我如何选择1.8V 或3.3V 的逻辑电平?

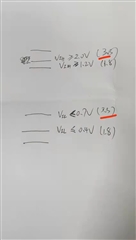

2) 2)此外、我不知道为什么在数据表中、它 仅显示1.8V 逻辑电平、因为我知道3.3V 逻辑电平是:VIL <= 0.7V、VIH >=2.0V。

此致、

非

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.