尊敬的技术支持团队:

我对 ADC3643有六个问题。

Q1在数据表第43页的8.5中、说明它可以在默认模式下运行、而不受 SPI 控制。 默认接口模式是什么?

该器件主要使用串行编程接口(SPI)进行配置和控制、但也可以使用串行编程接口(SPI)进行配置和控制

在不需要 SPI 接口的情况下以默认配置运行

Q2 是寄存器的默认值是否是每个寄存器值表的复位列中列出的值?

此外、默认状态是否与寄存器中的默认值不同?

(例如、在地址0x07的[2:0]上、表示返回000、直到它被 SPI 写入)。

Q3 DCLKIN 在 SPI (IN、OUT、Hi-Z)中选择双线模式之前、引脚的状态是什么?

如果在电源打开时输出、我们是否需要能够避免输出冲突?

Q4 关于第51页寄存器0x13的位0说明、在"... 寄存器0x07以及电子保险丝负载(0x12、D0)..." 0x13的拼写错误?

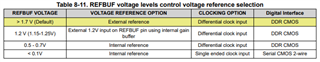

Q5 关于 REFBUF、如果差分时钟由外部基准设置而2Wire 模式由 SPI 设置、那么第43页的8.5.1是否特别不相关?

此外、在 SPI 中进行上述设置时、是否建议在 REFBUF 引脚的电路上进行处理?

第 64页的 Q6 InitializeSetUp 需要200、000个时钟进行校准。 我目前是否需要 DCLKIN?

此致、

TTD