主题中讨论的其他器件: ADS131E08

大家好、

我将 ADS130E08用于我的应用、以3ksps 的速率同时对6个通道进行采样。 我的问题是、

如何计算 SPI 时钟从 ADC 读取数据所需的时钟频率?

2.数据表中规定的 SCLK 和 CLK (主时钟)之间的区别是什么?

如何将 ADC 的采样频率更改为所需的值、如3ksps 或5ksps?

4.如果使用内部时钟、是否需要使用 CLK?

此致、

葡萄园

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

我将 ADS130E08用于我的应用、以3ksps 的速率同时对6个通道进行采样。 我的问题是、

如何计算 SPI 时钟从 ADC 读取数据所需的时钟频率?

2.数据表中规定的 SCLK 和 CLK (主时钟)之间的区别是什么?

如何将 ADC 的采样频率更改为所需的值、如3ksps 或5ksps?

4.如果使用内部时钟、是否需要使用 CLK?

此致、

葡萄园

您好、Vineyeth、

欢迎访问数据转换器论坛! 我将不按顺序回答您的问题、因为这样会更好地传递信息。

问题2.

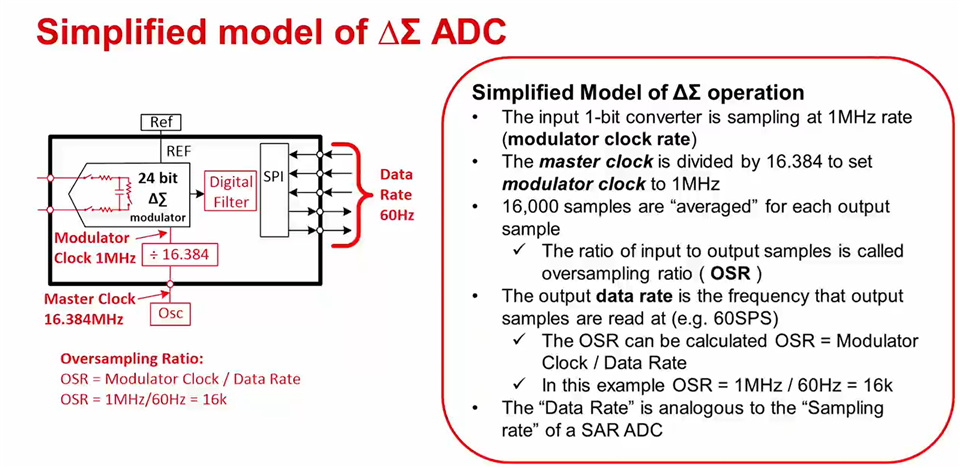

我强烈建议您观看有关 ADC 的 TI 高精度实验室视频系列、以开发您的专业知识。 我从基本操作迷你系列(大约8:36)中获取了这张幻灯片 :https://training.ti.com/ti-precision-labs-sar-delta-sigma-basic-operation

如您所见、Δ-Σ 需要一个主时钟(以前称为主时钟)、该时钟可以是外部时钟或内部时钟、然后降压到调制器时钟、然后进一步降低到数据速率。 但是、数据速率通常不是客户的可选参数、但 OSR 是、 可以通过计算来了解数据速率。

这与 SCLK 无关、因为调制器在转换时持续工作、并且使用 SPI 接口从 寄存器中实际获取转换结果。 这将回答 您的第二个问题。

问题3和4.

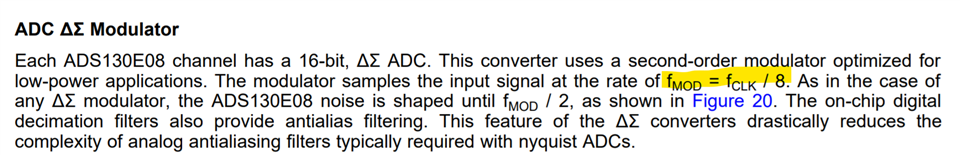

此时、您只需通过数据表查找这些值即可。 我将以 ADS130E08数据表为例进行分析:

![]()

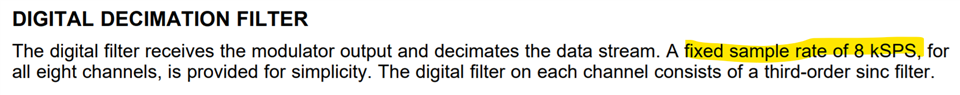

我想首先指出有关"8ksps"固定 采样率文本的文本。 如果使用内部振荡器来生成主时钟(f_CLK)、这是令人困惑的、但事实是这样。 如果我要更改文本、我会明确指出 OSR 和调制器时钟(f_MOD)调节在器件内是恒定的、如果用户想要从8kSPS 采样率进行更改、则必须更改为外部时钟模式。

这解释了内部振荡器频率预期 f_CLK (或主时钟)为2.048MHz 而不是一个值范围的原因。 通过使用其余信息、我们了解到 f_MOD (或调制器时钟)为256kHz (或2.048MHz/8)。 这样、我们就可以发现 OSR 为32 (或256k/8k)。

因此、如果我需要3kSPS、我将需要 96kHz (或32*3k)的 f_MOD、这会导致768kHz 的 f_CLK。 我将让您计算5kSPS 所需的值

与 ADS131E08相比、您可以知道输入时钟范围更宽、并且有一个 OSR 寄存器位、因此您应该保持一个恒定的 f_CLK 并更改 OSR 以在不同的采样率之间快速变化。

问题1.

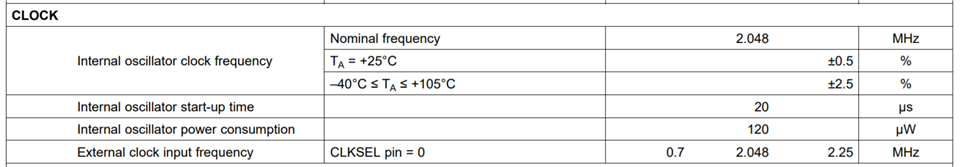

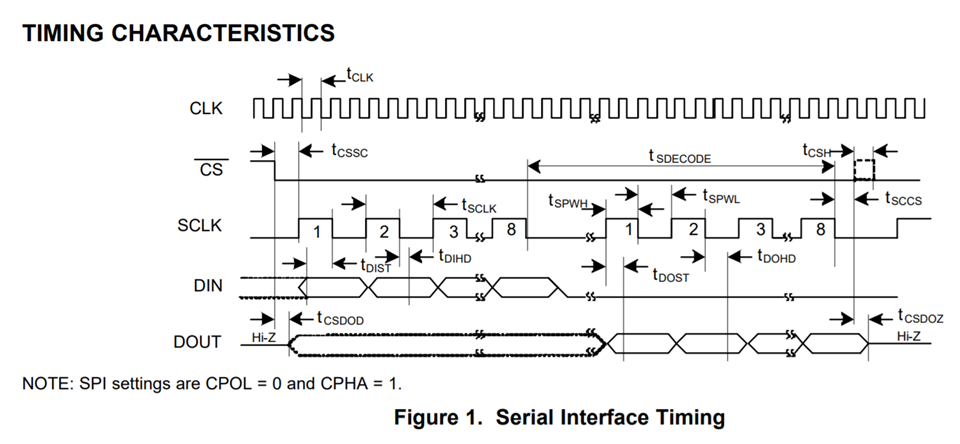

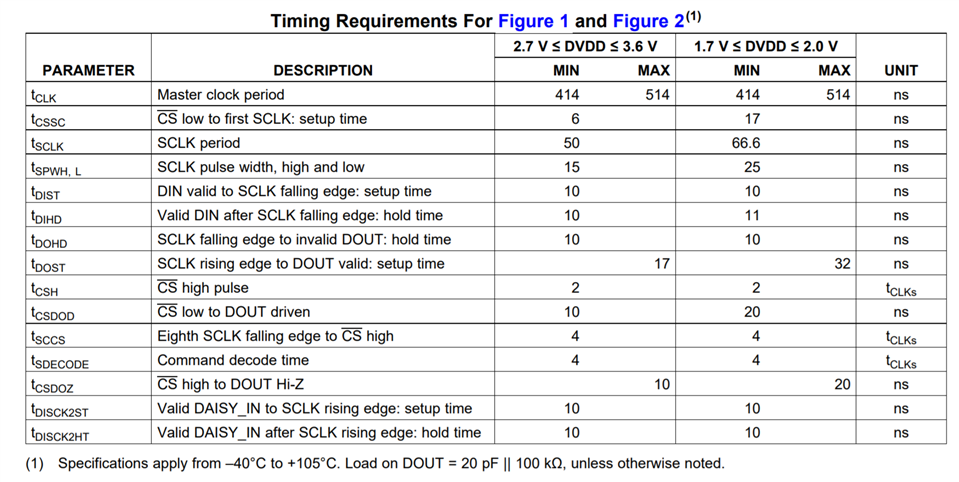

最后、我要说、我们对 SCLK 应该是什么有两个限制。 第一个限制是它不能超过20MHz (1/50ns)。 电气特性部分对此进行了概述。

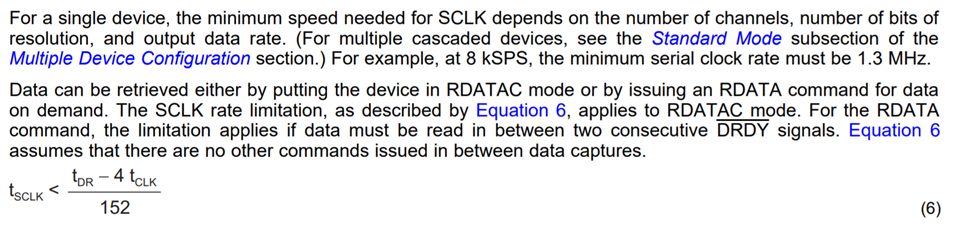

另一个制约因素是、我们需要在下一次转换完成之前超时所有数据。 数据表中有一个很好的段落:

如果您愿意、我会向您介绍 ADS131E08是 ADS130E08的直接替代产品。 ADS131E08有更好的文档记录、没有 奇怪的数据格式问题。 ADS130E08 的 设计初衷是简单、 并在设计时考虑到了8kSPS 的具体要求。 如果您不介意复杂性更高但灵活性更高、ADS131E08会更好。

最棒的

Cole