主题中讨论的其他器件: TI-JESD204-IP、 LMK04828

尊敬的 TI:

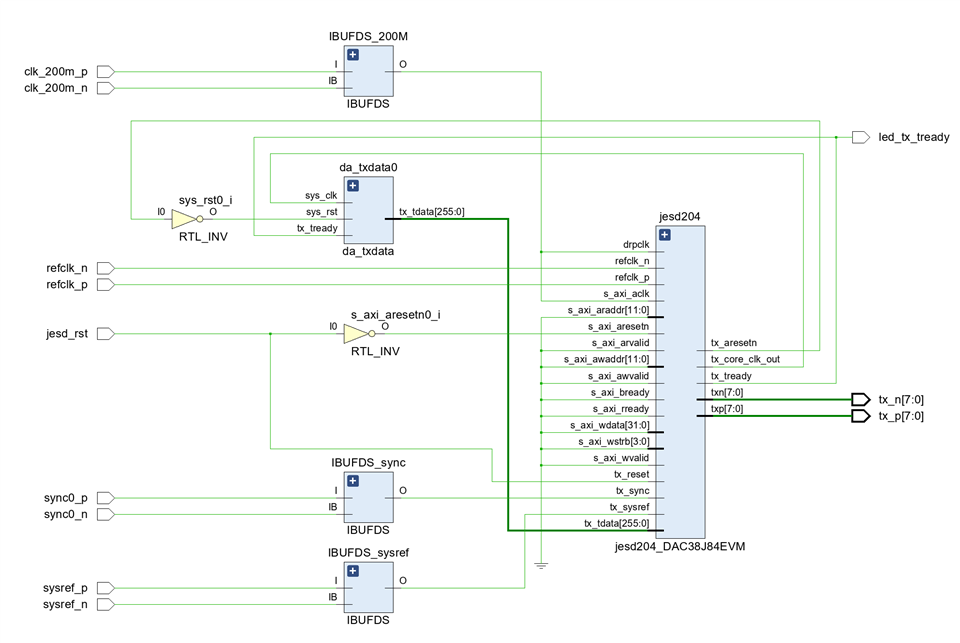

我正在使用 Xilinx FPGA kcu040 kintex UltraScale 来驱动 DAC38J84EVM、所有引脚都应该已正确分配。

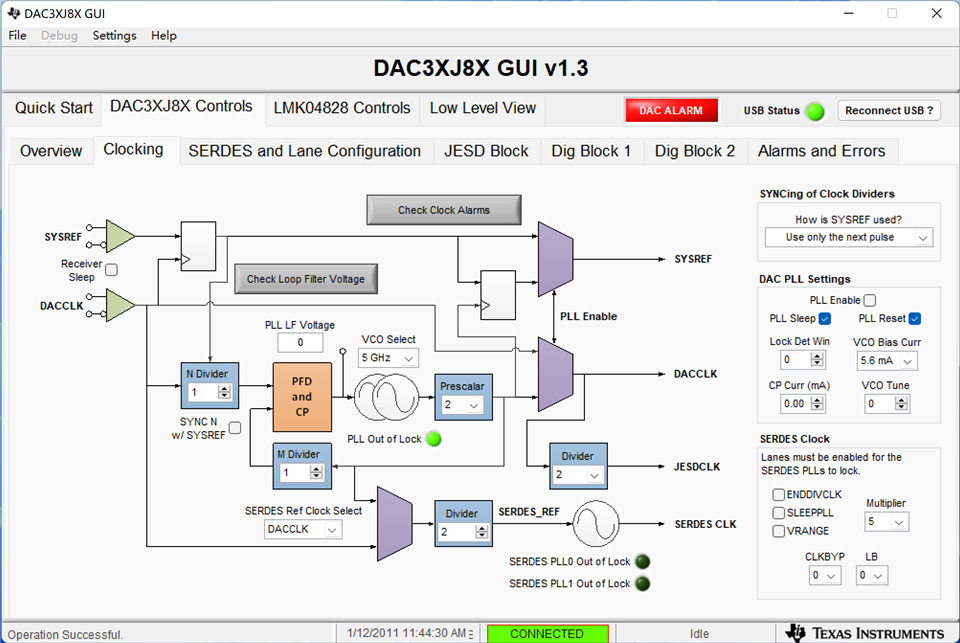

我已经尝试过 TI-JESD204-IP 和 Xilinx JESD204 IP。(当我使用 TI-JESD204-IP 时、我阻止了 ADC 输出和 ADC 输入)。两种设计最终都发出相同的"DAC 警报"- DAC PLL 失锁。

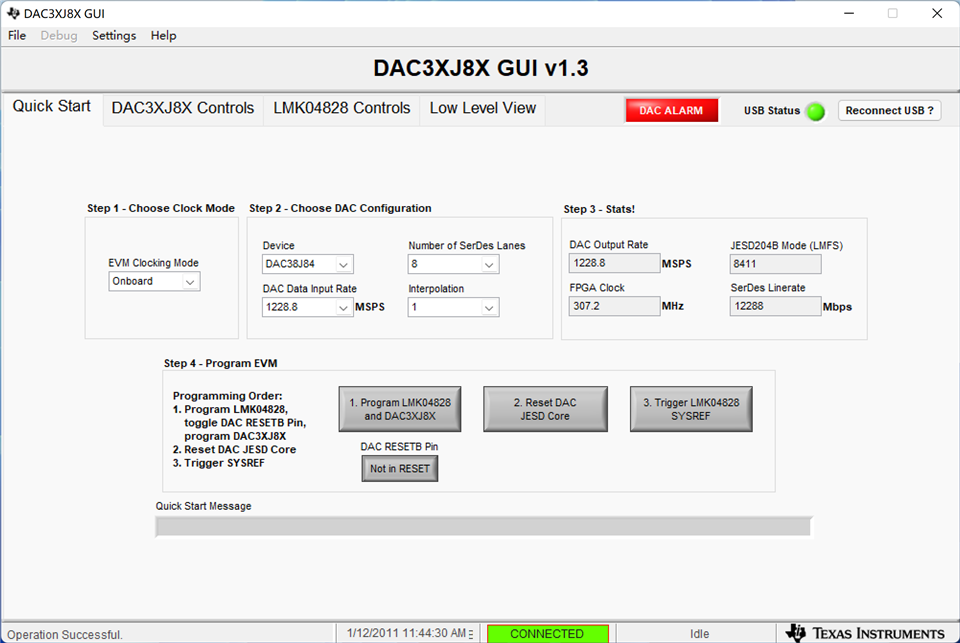

我的配置为:

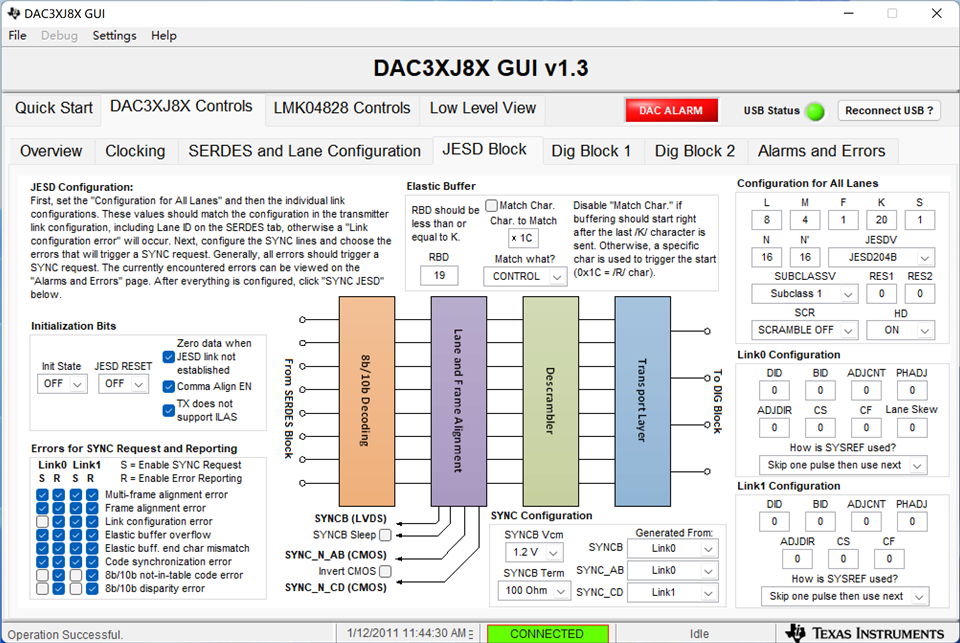

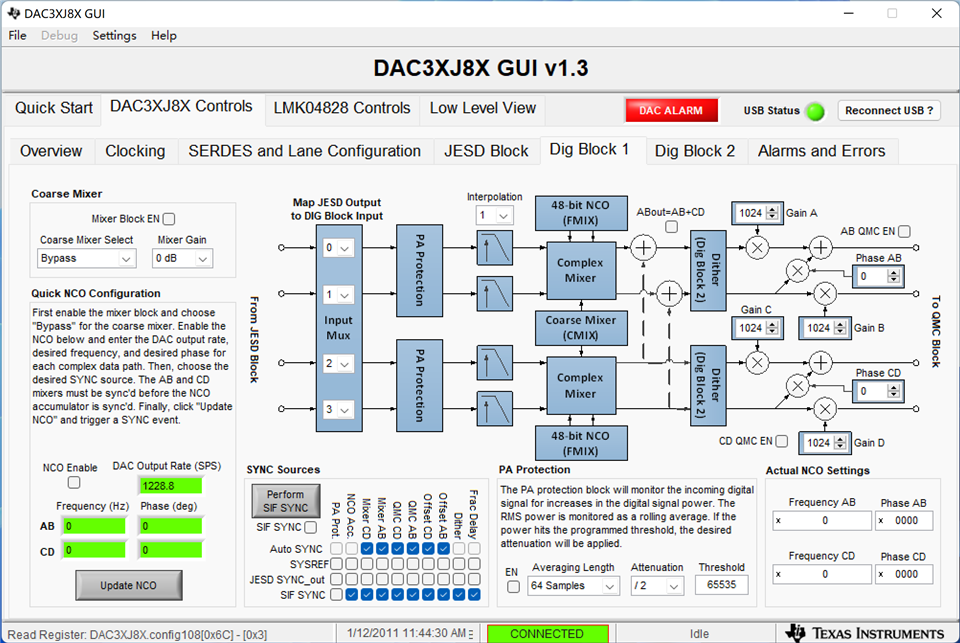

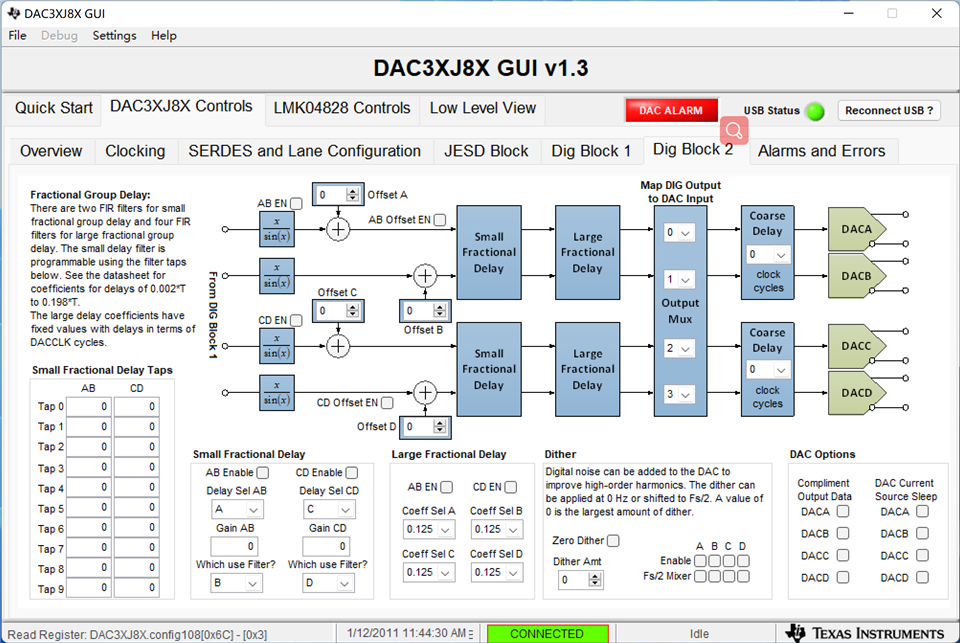

LMFS:8411

采样率:1228.8MSPS、

内插:1.

其他详细设置由 DAC3XJ8XEVM 指南手册 第4.3章"AC3XJ8X 快速入门程序"之后的"快速入门"页面自动生成。

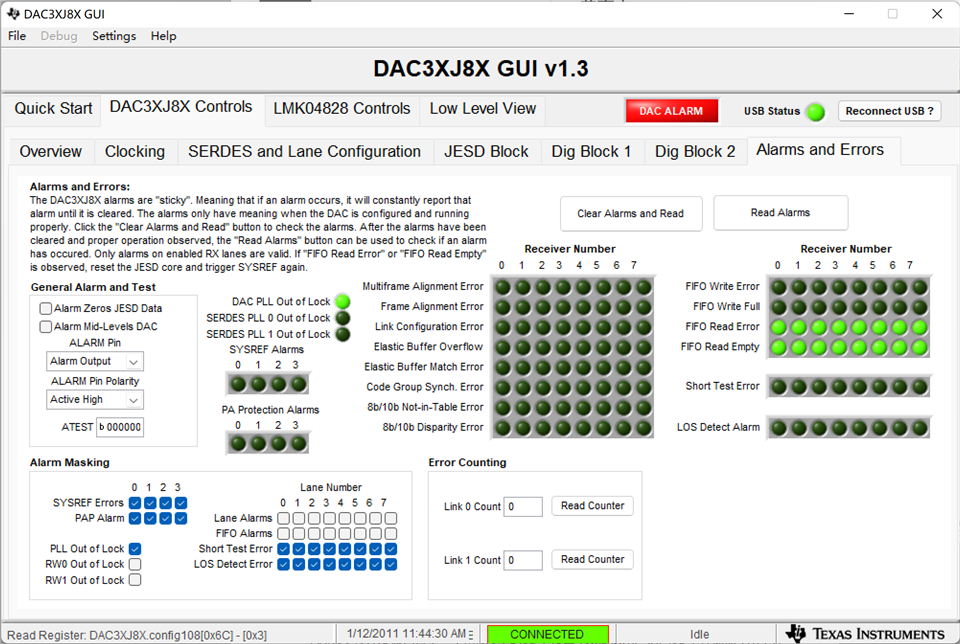

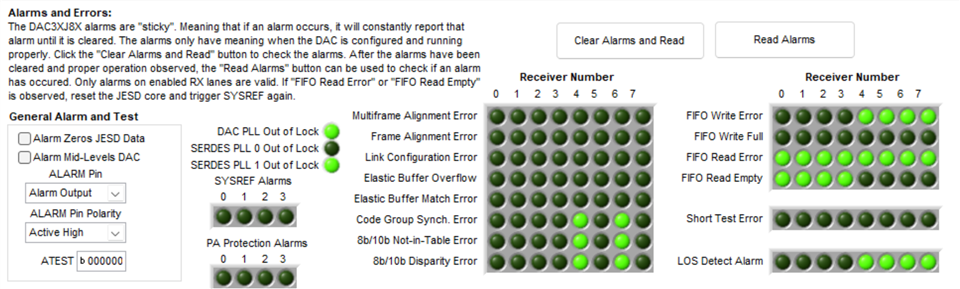

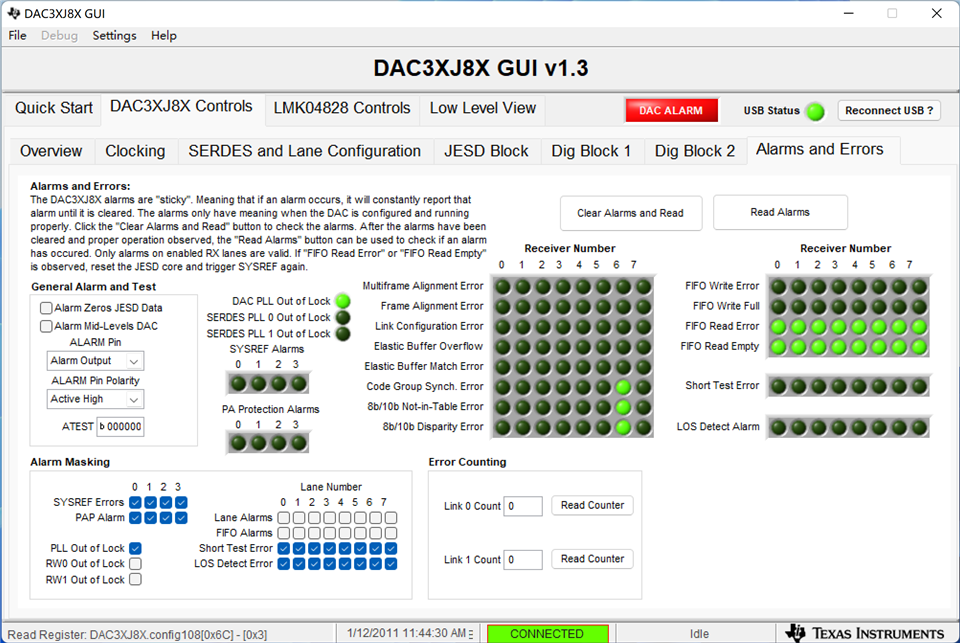

警报和错误页面:

这是我从"低级视图"页面e2e.ti.com/.../cfg.cfg 下载的 cfg。

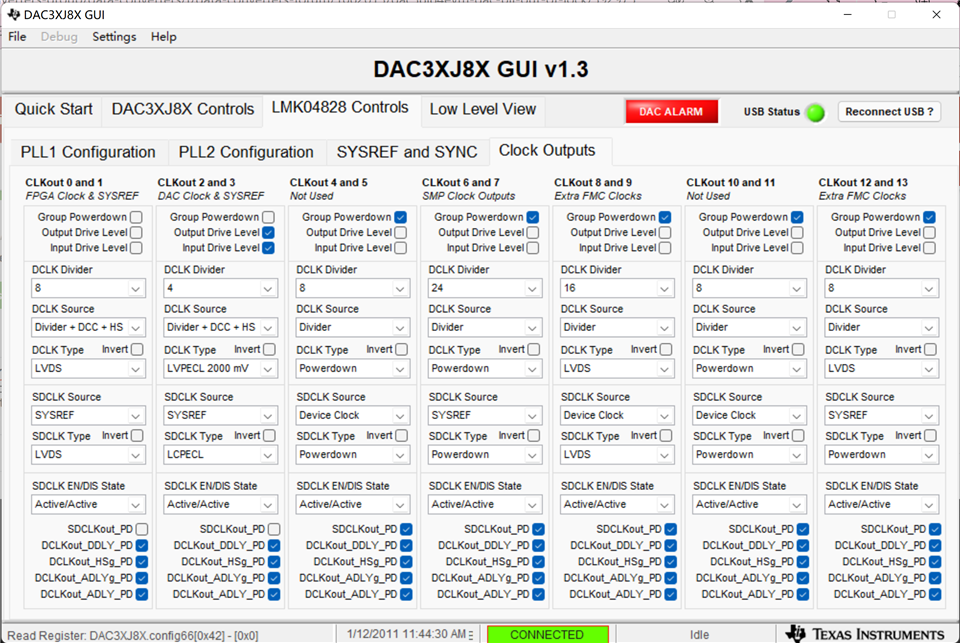

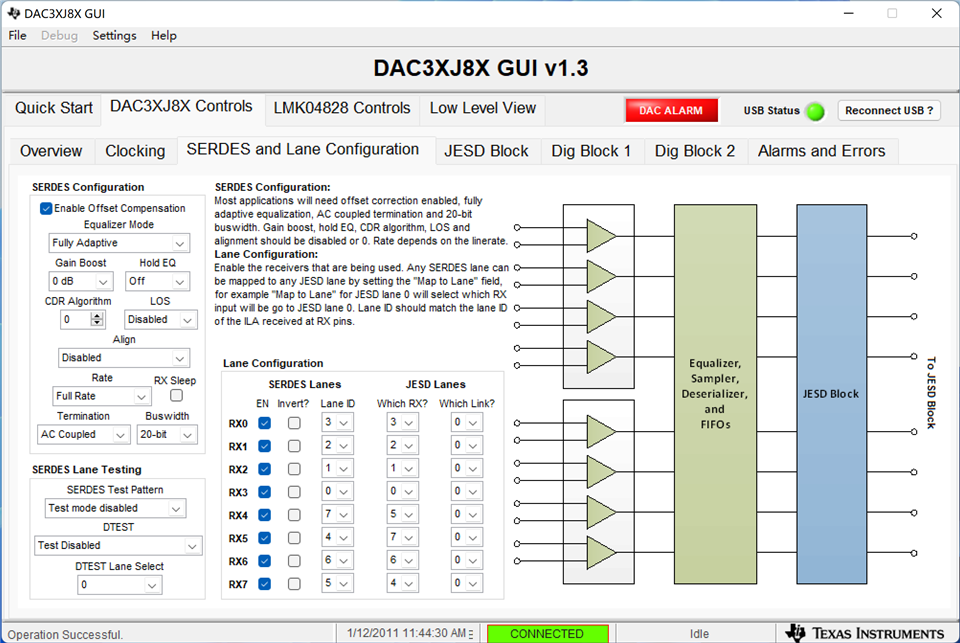

一些详细设置:

我在论坛上搜索了一些帖子、但它们的配置与我的不同。 我尝试跟随一些帖子、但失败了。似乎我必须设置 PLL_vcosel、PLL_VCO ...但我没有找到正确设置参数的位置和方法

请帮助我配置设置。