Other Parts Discussed in Thread: ADS42JB46

大家好、

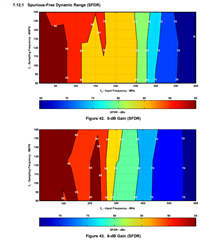

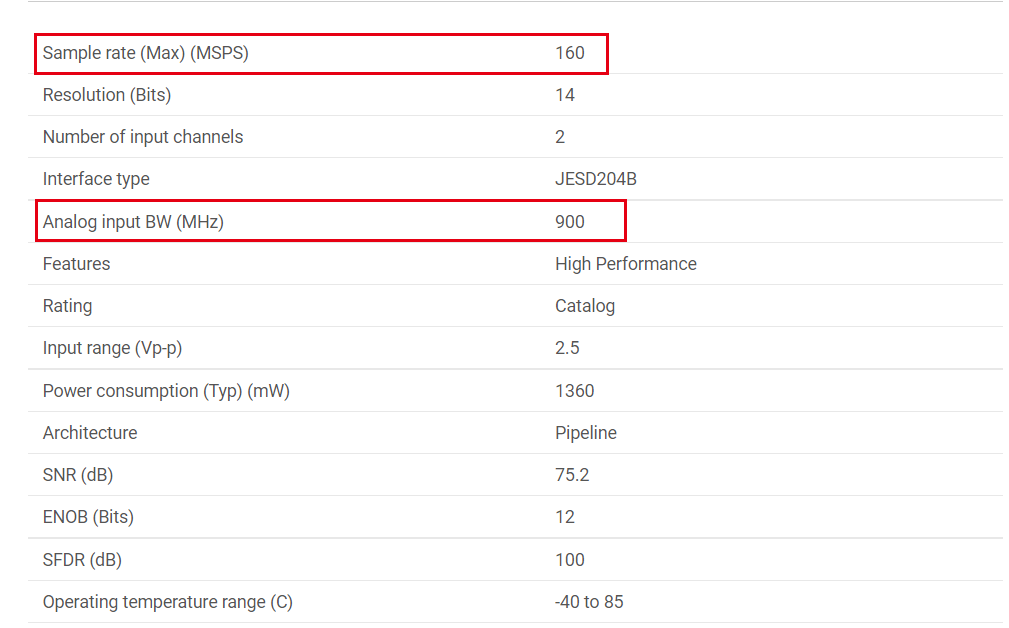

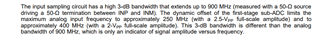

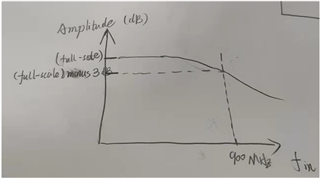

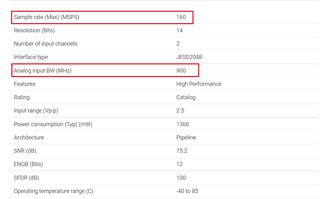

我不知道 为什么输入模拟带宽大于 ADS42JB46的采样率、ADS42JB46的模拟带宽约为900MHz、但其最大采样率为160MSPS、

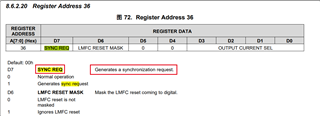

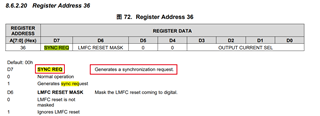

我对 JESD204B 有疑问、为什么 ADS42JB46 在 SPI 寄存器映射中具有"SYNC REQ"选项、地址为"0x36"。 我的问题是、这个"请求"信号用于什么? 我找不到任何用于"同步请求"的 I/O 端口?

那么、这种"请求"信号传输到哪里呢?

此致、

非