请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADC3664EVM 您好、E2E、

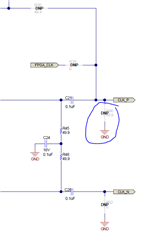

假设通过 FMC 连接器的采样时钟信号(来自 FMC 连接器 H4引脚的 FPGA_CLK 信号输入)输入的电压设计是多少?

如果您在电路图中以 VADJ-2.5V 为基准输入2.5V 单端时钟、它将超过 AD 转换器的额定电压(2.1V)。

由于放置了电平转换器、因此 SPI 信号等似乎可以输入2.5V、但采样时钟似乎直接连接到 AD 转换器。 是否可以认为输入为1.8V 单端信号是正确的用法?

此致、

ACGUY