e2e.ti.com/.../AFE5832DEBUG2021_5F00_1103.docx

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

e2e.ti.com/.../AFE5832DEBUG2021_5F00_1103.docx

您好、Ao、

我们希望将此对话脱机、因为器件 AFE5832包含在选择性披露中。

您能否联系 support_us_afe_tx@list.ti.com 并参考此 e2e 帖子?

Praveen Aroul、您好!

AO 帮助我发送了这个问题、我补充了一些内容

我给出了 ADC 时钟80MHz。 设置12位、x1速率。

1) 1) I SerDes FCLK by DCLK,值1111111100000000在同步模式下非常稳定。 但不处于斜坡模式。

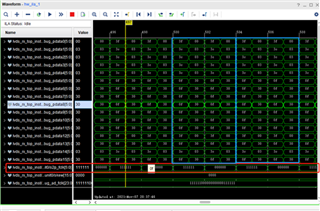

在同步模式下、fclk 稳定地:

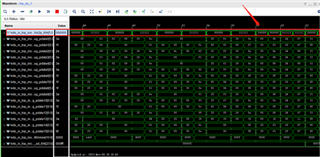

在斜坡模式下、fclk 不可避免地:

2) 2)我的上电序列按 Ao 显示,您能帮我检查一下吗?

3) 3)我尝试了两种方法来处理串行器/解串器 LVDS 数据、如下所示:

(1)我使用同步测试模式111111000000,然后在中设置延迟时间并对数据线进行位滑动。 之后,它可以很好地匹配该值,但更改到斜坡模式后数据出错。

(2) I SerDes FCLK、bitslip FCLK 和数据、以使 FCLK 匹配1111111100000000。 但同一芯片中的数据不同。

4)正确的电源序列是什么?

我期待你的答复。 谢谢。

您好 Lucas、

您能否将查询发送至邮件列表 support_us_afe_tx@list.ti.com?