主题中讨论的其他器件: CDCE72010

您好!

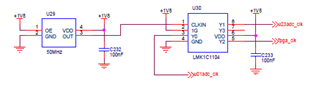

我使用1.8V CMOS 单端时钟来驱动 ADS4222时钟输入。

由于 CLK_M 连接到 VCM (0.95V)、它是否应使 CLK_P 超过1.8V? 有任何风险?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Xiaoc强、

LVCMOS 单端交流耦合配置的建议输入时钟振幅为1.5V。(请参阅此处数据表的第11页: https://www.ti.com/lit/ds/symlink/ads4222.pdf?ts=1634850418269&ref_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FADS4222)

此致、Amy

您好、Xiaoc强、

TI 网站上提供了大量时钟缓冲器供您选择。

如果您让我们更详细地了解您的需求、我们可以帮助您进行选择。

否则、请查看下面的链接、您将可以开始使用该链接。

此致、

Rob