主题中讨论的其他器件: TSW54J60EVM

您好!

我使用了 TSW54J60EVM (用于评估 ADS54J60)以及具有 JESD204IP 的 Xilinx 演示板。 我已使用正确的 PLL/JESD 设置获得有效的 ADC 数据。 采样率为983.04MHz、帧模式为8224、sysRef 分频器为768。

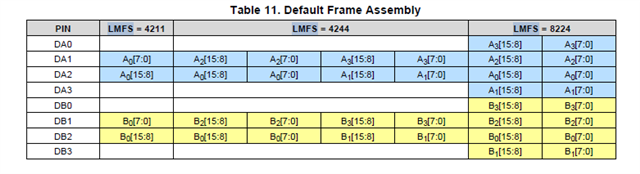

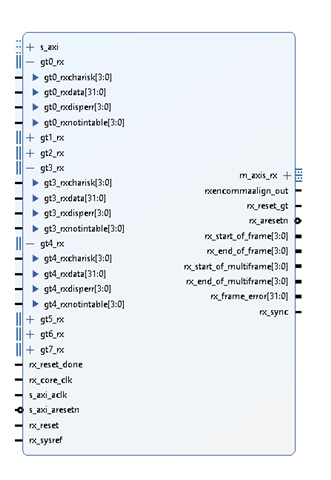

但是、我很难获得校正器 ADC 字顺序。 在 FPGA 侧、对于每个模拟通道、有8个字:对于通道 A、gt0[31:0]至 GT3[31:0];对于 gt7[31:0]、GT4[31:0]至 gt7[31:0]。 对于每个通道、有8个16位字。 这8个字的顺序是什么? ADS54J60上是否有用于定义该序列的寄存器? 例如,A3[31:16]是否早于 A3[15:0]? A2[15:0]是否早于 A1[15:0]? 如果没有正确的 ADC 字序列、对于正弦波形、我得到的正弦波形每8个字中都有锯形。

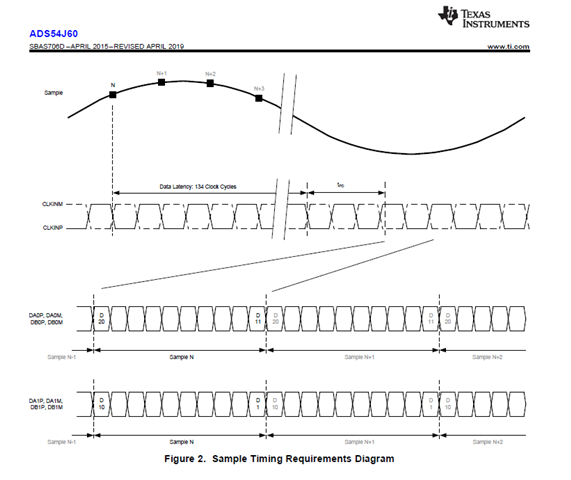

从 ADS54J60数据表中、我发现图2显示了 N 个样本、N+1个样本。 但它不显示哪个通道(DA0或 DA1)具有较早的样本。

第二个问题是16位字内的字节顺序、我不知道如何控制它并观察到随机字节顺序。 例如、对于 A3、校正器字节顺序可以是 A3[31:16]和 A3[15:0]。 对于同一帧、A2字节顺序为 A2[23:16、31:24]和 A2[7:0、15:8]。 我尝试在 GUI 中使用"触发 ADC 数据"、但它似乎无法完全控制一个16位字中的字节顺序。

提前感谢您的任何建议。

-Yuke

ADS54J60数据表中的采样图

ADS54J60中的表11

Xilinx 端的 JESD204B