Other Parts Discussed in Thread: DAC3171, DAC3174

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

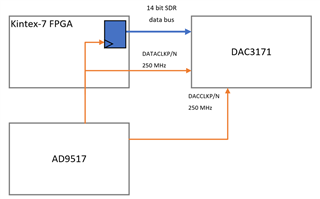

器件型号:DAC3171 大家好! 我们使用具有 Kintex-7 FPGA 的定制板和具有14位数据总线的 DAC3171 (FS = 250MHz、 二进制补码)。 在 DAC3171设置期间、我们注意到低7个数据引脚(D[6:0])对输出模拟信号没有影响。 只有当数字信号电平超过127 (占用超过7 LSB 位)时、我们才能看到模拟输出发生变化-这就是问题所在。 似乎只有7个 MSB 引脚(D[13:7])工作。

我们已经完成了几项测试:

测试1. 使用 CONFIG20寄存 器、我们尝试根据 sifdac 值更改恒定模拟输出。 从0升至127、我们一直看到相同的极低直流信号。 在 D[7]不再成为符号位后、模拟信号也开始上升。 我们使用示波器测量输出电压

测试2. 我们将 iotest 与来自 FPGA 的8个不同图形和8个具有 SYNC 信号的相同图形结合使用。 根据 CONFIG4 = 0x0000 (该寄存器在测试期间被清零)、所有引脚都成功通过了测试。 在任何模式中发生错误都会使所需的引脚无法按预期通过测试。

测试3. 尝试从 FPGA 传输不同的常量、我们也没有成功处理 D[6:0]。 只有7个 MSB 位(D[13:7])工作正常。

我们使用数据表中的加电序列来配置 DAC (在上一修订版中为7.5.1第38页)。

引脚睡眠、TXENABLE 和 RESETB 由 FPGA 良好控制(使用示波器进行测试)。 时钟 DATACLKP/N 和 DACCLKP/N 在 DAC 配置开始前配备来自 AD9517的250MHz 时钟。 观察到数据总线时序(FPGA 将 DATACLKP/N 信号延迟1ns 以将上升沿移至数据中心)。 根据 数据表、ALIGN = DIGVDD18、ALIGN = GND、因为我们不使用它们。 SYNCP = 0、 SYNCN = 0 by FPGA、因为我们使用 sif_SYNC 功能实现 DAC 内部 FIFO 同步。

很少有人遇到同样的问题:

https://e2e.ti.com/support/data-converters-group/data-converters/f/data-converters-forum/416334/dac3171-configuration-problem (问题相同)

https://e2e.ti.com/support/data-converters-group/data-converters/f/data-converters-forum/536109/dac3171-with-incorrectly-programd-fuses

https://e2e.ti.com/support/data-converters-group/data-converters/f/data-converters-forum/416232/dac3171-7-bit-interface-mode

内部 DAC 保险丝有问题吗? 我们的 DAC3171标记为:

TI 83J

PJ5J G4

使用 TI DAC3174 EVM GUI 生成的此类寄存器值:

{addr=0x00、data=0x46e4}、

{addr=0x01、data=0x600f}、

{addr=0x02、data=0x3fff}、

{addr=0x03、data=0x0000}、

{addr=0x04、data=0x0000}、

{addr=0x05、data=0x0000}、

{addr=0x06、data=0x0000}、

{addr=0x07、data=0xFFFF}、

{addr=0x08、data=0x6000}、

{addr=0x09、data=0xe000}、

{addr=0x0a、data=0xf080}、

{addr=0x0B、data=0x1111}、

{addr=0x0c、data=0xFFFF}、

{addr=0x0d、data=0xFFFF}、

{addr=0x0E、data=0xFFFF}、

{addr=0x0F、data=0xFFFF}、

{addr=0x10、data=0xFFFF}、

{addr=0x11、data=0xFFFF}、

{addr=0x12、data=0xFFFF}、

{addr=0x13、data=0xFFFF}、

{addr=0x14、data=0x8000}、

{addr=0x15、data=0x0000}下面是我们板的简化版原理图(睡眠、TXENABLE 和 RESETB 也连接到 FPGA):此致

Nick H.