Other Parts Discussed in Thread: ADS5482

您好 TI 团队

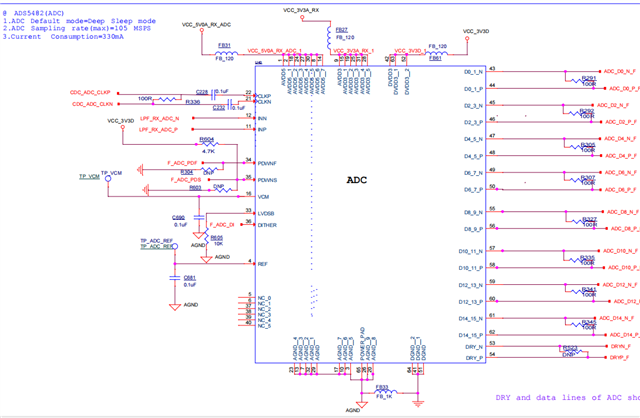

我们在设计中使用 ADS5482 ADC。 我们的信号带宽为500kHz 至20Mhz。 ADC 时钟频率为105Mhz (LVDS)、我们以105MSPS 运行 ADC。 我们使用内部基准电压。

但是当我从万用表探测输入引脚时,其输入基准引脚电压不是恒定的,并且在0v 到3.1v 之间波动。 为了使 ADC 的输出稳定,其输入电压上的基准电压应该是稳定的3.1V。 为什么会发生这种情况?

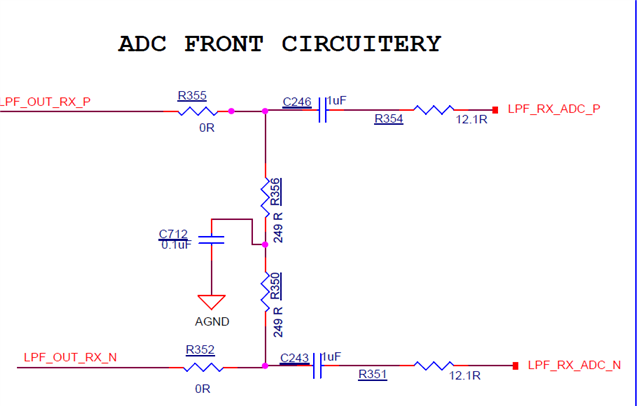

ADC 前端输入引脚电路的 PFB 图像

PFB ADC 原理图图像

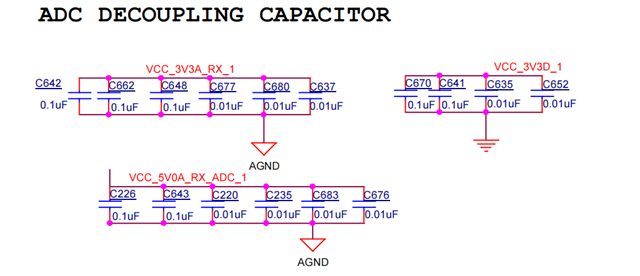

PFB 去耦电容器图像

请建议一些评论要点以解决此问题。