主题中讨论的其他器件: DAC38J84EVM、 LMK04828

你(们)好。

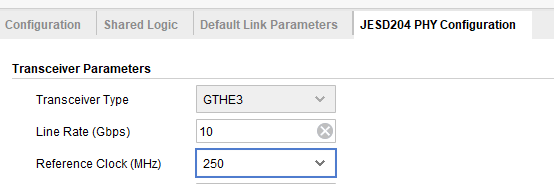

我们有一个工作系统、其中包含 Xilinx Ultrascale FPGA JESD204 TX 到 DAC38J82。 FPGA JESD 配置为8通道、通道速度为10Gbps。 对于250MSPS、DAC 和 FPGA JESD204的参考时钟均为250MHz。 Sysref、位于 7.8125Mhz。

现在 、为了支持符号速率较低、为150MSPS 或175MSPS 的系统、我们开始重新配置 FPGA JESD204和 DAC。 FPGA JESD 具有8条通道、速率为6Gbps、参考时钟为150Mhz。 SYSREF、频率为6.25Mhz。 但现在 SYNC 信号不会生效。