您好~

当使用 DAC37J84更改采样率时、,JESD204B 协议可在采样率 为1200MSPS 1000MSPS 600MSPS 500MSPS,时建立、但 无法在采样率低于500MSPS(400MSPS 300MSPS 250MSPS 240MSPS 200MSPS)时建立

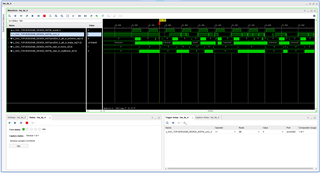

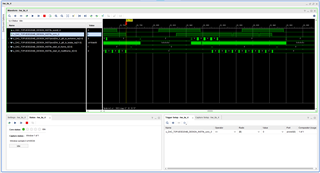

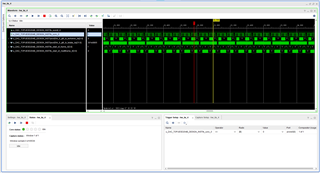

具体性能如下:首先完成 CGS、ILAS 和用户数据传输的协议建立、然后等待几秒钟后用户数据传输的建立失败。 之后、SYNC 信号有时会降低脉冲、有时会降低几纳秒、从而导致协议的不稳定建立、如下图所示。

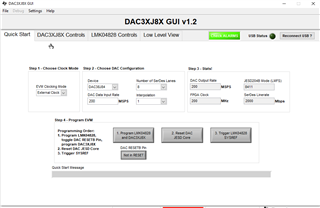

我的200MSPS 采样率 DAC 配置 如下所示

FPGA:XCKU040-FFVA1156-2-I

L M F S HD:8 4 1 1 1

DAC 输入速率:200MSPS

通道速率:2Gbps

内插:1x

我在下面添加了配置。

8'hFF、16'h0000

8'h00、16'h0018

8'h01、16'h00A3

8'h02、16'h2002

8'h03、16'hA300

8'h04、16'h0000

8'h05、16'hFF03

8'h06、16'hFFFF

8'h07、16'h1E00

8'h08,16'h0000

8'h09,16'h0000

8'h0A、16'h0000

8'h0B、16'h0000

8'h0C、16'h0400

8'h0D、16'h0400

8'h0E、16'h0400

8'h0F、16'h0400

8'h10、16'h0000

8'h11、16'h0000

8'h12、16'h0000

8'h13、16'h0000

8'h14、16'h0000

8'h15、16'h0000

8'h16、16'h0000

8'h17、16'h0000

8'h18、16'h0000

8'h19、16'h0000

8'h1A、16'h0020

8'h1B、16'h0000

8'h1E、16'h9999

8'h1f,16'h9980

8'h20、16'h8008.

8'h22、16'h1B1B

8'h23、16'h01 FF

8'h24、16'h0020

8'h25、16'h2000

8'h26、16'h0000

8'h2D、16'h0001

8'h2E、16'hFFFF

8'h2F、16'h0004

8'h30、16'h0000

8'h31、16'h1000

8'h32、16'h0000

8'h33、16'h0000

8'h34、16'h0000

8'h3B、16'h0800

8'h3C、16'h0028

8'h3D、16'h0088

8'h3E、16'h0108

8'h3F、16'h0000

8'h46、16'h0120

8'h47、16'h3450

8'h48、16'h31C3

8'h49、16'h0000

8'h4A、16'hFF01

8'h4B、16'h1200

8'h4C、16'h1F07

8'h4D、16'h0300

8'h4E、16'h0F6F

8'h4F、16'h1C61

8'h50、16'h0000

8'h51、16'h00DC

8'h52、16'h00FF

8'h53、16'h0000

8'h54,16'h00fc

8'h55,16'h00ff

8'h56、16'h0000

8'h57,16'h00FF

8'h58、16'h00FF

8'h59、16'h0000

8'h5A、16'h00FF

8'h5B、16'h00FF

8'h5C、16'h6666

8'h5E、16'h0000

8'h5F,16'h0123

8'h60,16'h4567

8'h61、16'h0211

8'h64、16'h0000

8'h65、16'h0000

8'h66、16'h0000

8'h67、16'h0000

8'h68、16'h0000

8'h69、16'h0000

8'h6A、16'h0000

8'h6B、16'h0000

8'h6C、16'h0000

8'h6D、16'h0000

8'h6E、16'h0000

8'h6F、16'h0000

8'h70、16'h0000

8'h71、16'h0000

8'h72、16'h0000

8'h73、16'h0000

8'h74、16'h0000

8'h75、16'h0000

8'h76、16'h0000

8'h77、16'h0000

8'h78、16'h0000

8'h79、16'h0000

8'h7A、16'h0000

8'h7B、16'h0000

8'h7C、16'h0000

8'h7D、16'h0000

8'h4A、16'hFF1E

8'h4A、16'hFF1F

8'h4A、16'hFF01

RBD 已调整为8、16、24、28和32、但低于500MSP 的采样率时仍然存在此问题

读取寄存器0x64~0x6B 后、发现如果该值高于500MSPS、则为0000。 如果该值低于500MSPS、则有三种可能:0002、0100和8100、但无法找到问题的原因

此外、由于 FPGD_DCLK 和 GTH CLK 需要随着采样率的变化而切换、FPGA 约束将这两个时钟限制为1200MSPS 的采样率(如下所示)、不确定这是否会导致问题(实际上、 我们尝试使用 FPGD_DCLK 和 GTH CLK 时钟限制将其限制为200MSPS、两者均为100MHz、但无法建立200MSPS 的协议。)

create_clock-period 3.333-name jesd204_DAC_REFCLK [get_ports refclk0p]

CREATE _CLOCK -PERIOD 1.667-NAME GLBLCLKP [GET_PORTS GLBLCLKP]

此外、本设计中的最大线速率为12Gbps、但使用了 FR4材料。 它是否会引起问题尚不确定(但如果是重大问题、为什么在建立低频协议失败的情况下建立高频协议是正常的)。

感谢你的帮助