主题中讨论的其他器件:LMK04832、

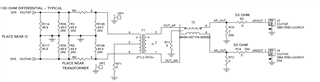

e2e.ti.com/.../7776.DAC_5F00_LMK_5F00_Schematic.pdf

您好!

我们已使用器件型号为 DAC39J82IAV 的3个 TI DAC 生成模拟输出。 LMK04832NKDT 用于生成 JESD204B 时钟和采样时钟。

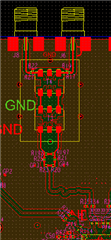

原理图部分已随附、请提供设计的审阅反馈。

设计使用详细信息:

- 所有 DACCLKP/N -交流耦合、LVPECL、2520MHz

- 所有 SYSREFP/N -根据通道速率和系统时钟频率设置、用于直流耦合的交流耦合选项、LVPECL (交流耦合) LCPECL (直流耦合)、<20MHz

- DAC WB、NB 模拟输出(U31)- OUTAP/N:407.5±30MHz、IOUTDP/N:70MHz±2.5MHz、

- DAC LO 1模拟输出(U32)- OUTAP/N:223.5 - 311.4MHz

- DAC 3模拟输出(U53)- OUTAP/N:405±37.5MHz

- 1 - 360MHz 的 LMK 时钟