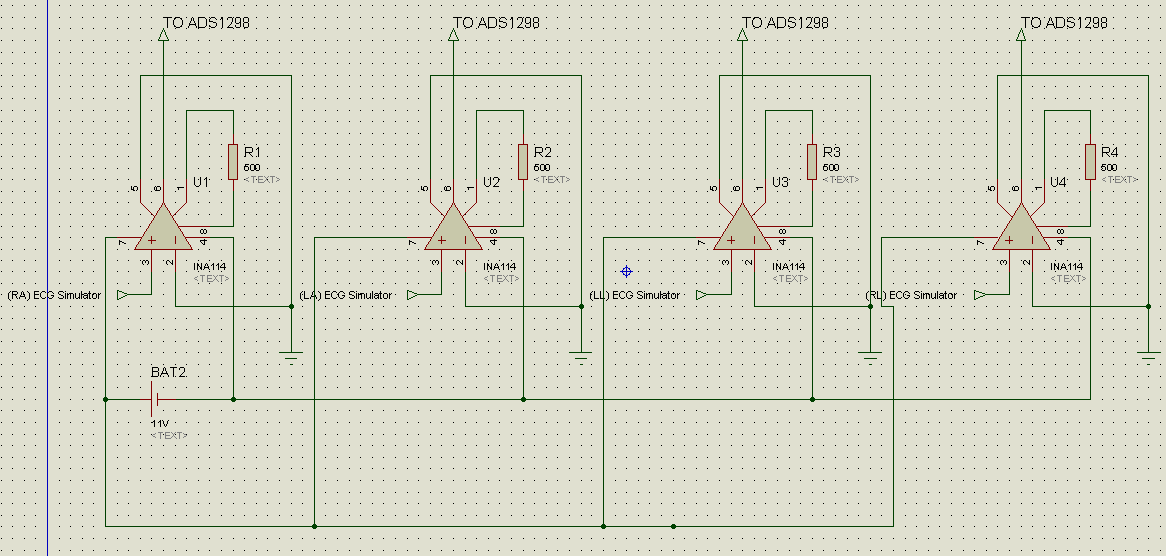

主题中讨论的其他器件:INA826S、 INA826、 INA114、 ADS1298、

您好!

我的项目需要非常低的输入参考噪声、理想情况下为1uV 峰值、但至少为5uV 峰值。

我正在考虑降低输入参考噪声的方法。 信号调节电路(从 AFE 输入到 ADC 输入)的输入参考噪声似乎是不可更改的。 但是、可以使用外部时钟(减少抖动)和外部基准(更高的电压精度)以及调整抗混叠滤波器的外部电容(以在考虑稳定时间的情况下实现所需的通道带宽)来降低 ADC 噪声。

但是、我计划使用 PGA 增益= 12、采样率 SPS=500、 由于知道 AFE 输入参考噪声= sqrt (VSC_rms^2+(Vadc_rm/PGAgain)^2)、其中 Vsc_rms 和 Vadc_rms 信号调节电路和 ADC 输入参考噪声电压 rms、ADC 噪声似乎只占 AFE 噪声的一小部分。

无论如何、我可以使用抖动为5ps 的外部时钟和初始精度为0.04%的外部基准、并且我会在80Hz 时调整3dB 通道带宽的外部电容。 我从数学角度了解了改变抗混叠滤波器如何改变输入参考噪声、但外部时钟和参考噪声则不是这样。

您知道输入参考噪声可以降低到哪个扩展范围吗?

谢谢