主题中讨论的其他器件:LMK04828

您好!

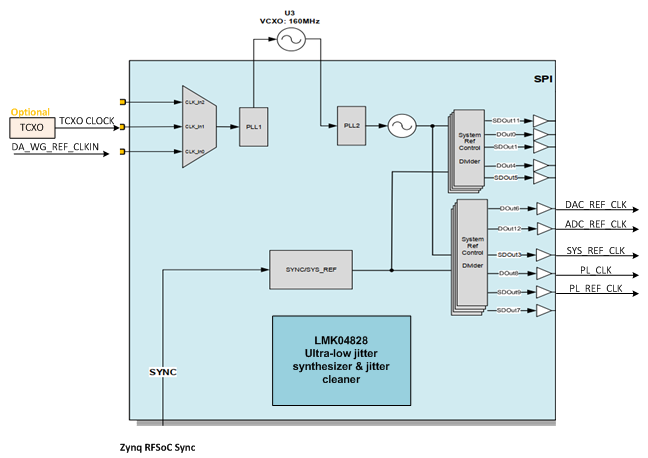

我们需要同步两个 ADC12DJ5200。 这两个器件的采样时钟由一个单一 PLL 生成、并且两个时钟走线长度在电路板上都是匹配的。 我们使用器件 LMK04828来生成 JESD204B 所需的器件和 SYSREF 时钟。 从 LMK 到 ADC 的 SYSREF 布线长度也是匹配的。 器件时钟和到 FPGA 的 SYREF 对也是长度匹配的。 我们在 JMODE 20中以5.2Gsps 的采样率操作 ADC

因此、在两个 ADC 之间捕获的数据的相位在每个功率周期中都有所不同。 请澄清 在初始化设置(第8.3节)的哪个阶段应该 完成数据表第7.3.6.3.2节中提到的自动 SYSREF 校准。

此致、

Ayesha