主题中讨论的其他器件: LMK04828、 LMX2592

您好!

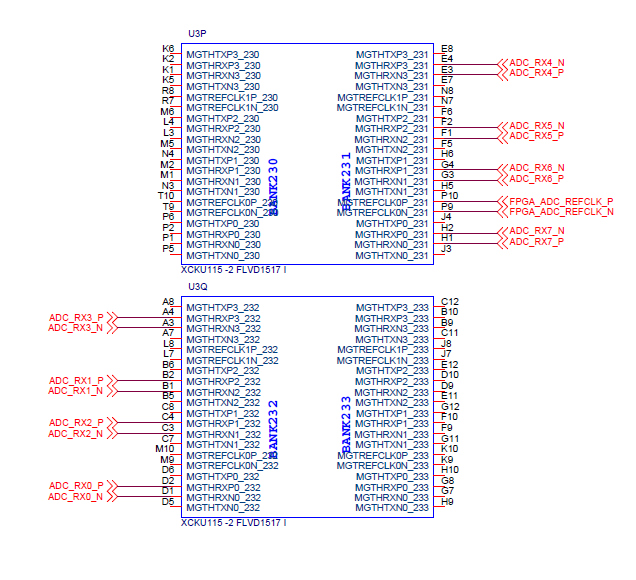

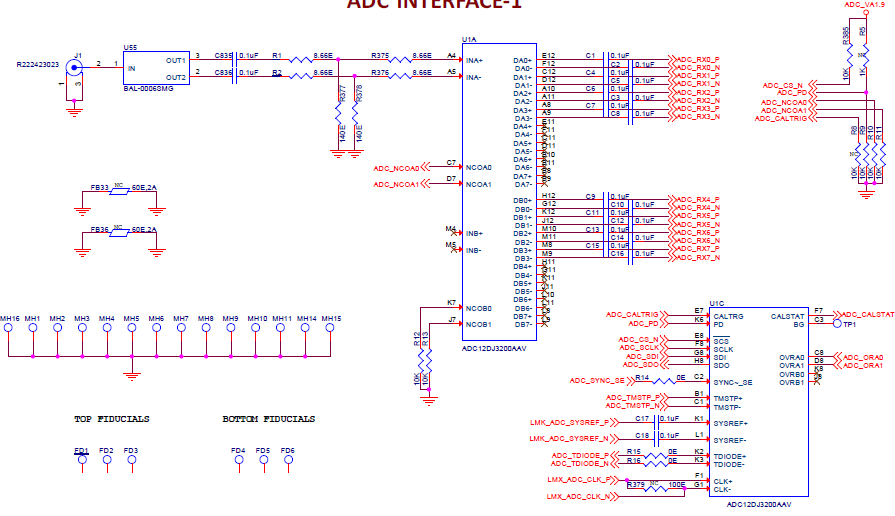

我们使用的 ADC12DJ3200在 JMODE 5下以5GSPS 的速率运行。 我们以6.25Gbps x 8通道的速率运行 SerDes。

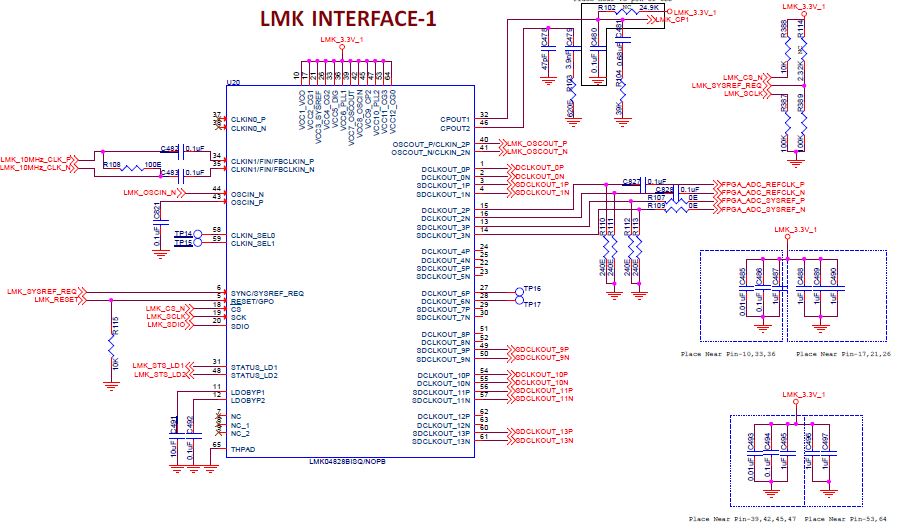

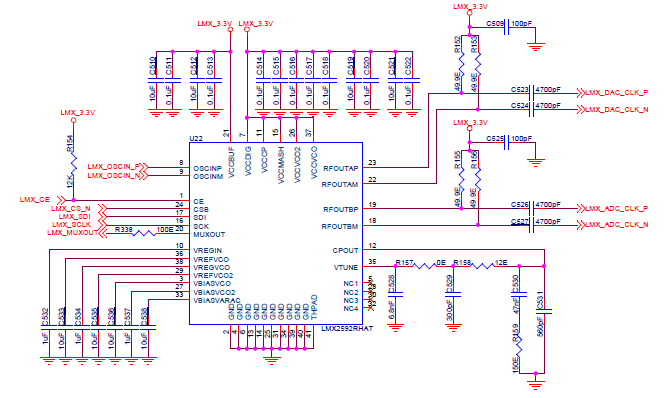

从 LMK04828生成的 FPGA 的 Sysref (19.53125MHz)和 Dclk (156.25MHz)以及从 LMX2592生成的 ADC 采样时钟(2.5GHz)。

ADC sysref 也可通过 LMK04828 (19.53125MHz)针对 F=1和 K=32生成。 FPGA 和 ADC 均采用相同的设置运行。

我们已经监控了 FPGA 的 dclk 和 sysref、我们正在 LVDS 中运行、并在 FPGA 规格内进行接收。

ADC 的 sysref 时钟与 LMK04828的 LVPECL (1600)搭配使用、电路与 ADC 评估板 HSP001类似。

我们能够读取和写入 ADC。 ADC 调试状态寄存器读取0x1C。 ADC 似乎响应正常。 但同步是低电平。

我们使用的是 PHY + JESP IP、FPGA 端接收一些垃圾数据、而不是0xBC。

请帮助、我们在这个阶段感到惊讶。

此致、

Rajesh Khanna