Other Parts Discussed in Thread: ADS7863A, ADS7863

主题中讨论的其他器件: ADS7863

大家好、团队、

我的客户知道这样一个事实、即 ads7863A 取代了旧版本、 并且他们在设计中使用了更新版本。 遗憾的是、它们无法从 ads7863A 的数据表中获得足够的时序信息。 它们似乎找不到任何有关 ADC 从 SDI 开始读取的边沿的信息、或者在 sdoa/b 上发送第一位

提前感谢。

此致、

Renan

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: ADS7863A, ADS7863

大家好、团队、

我的客户知道这样一个事实、即 ads7863A 取代了旧版本、 并且他们在设计中使用了更新版本。 遗憾的是、它们无法从 ads7863A 的数据表中获得足够的时序信息。 它们似乎找不到任何有关 ADC 从 SDI 开始读取的边沿的信息、或者在 sdoa/b 上发送第一位

提前感谢。

此致、

Renan

您好、Ryan、

感谢您的回答、但我仍有一些问题。

您说数据从第4个下降沿开始在 sdo 端口上计时。

数据表显示如下:

串行数据输出(SDOx)

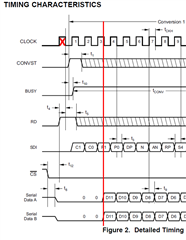

SDOx 管脚上转换后的数据在产生 RD 脉冲后的第3个下降时钟边沿生效。 以下各节详细介绍了不同的工作模式。

这意味着什么?

我是否可以假设 SDI 上的第一个位也在第4个下降沿锁存? 此外、ADS7863A 在上升沿将数据移入器件、在下降沿锁存 SDI、这意味着什么? 它是在下降沿还是上升沿移入数据? "数据移位"和"锁定数据"对我来说是相同的。

此致、

Renan

Renan、您好!

我的意思是、移位数据时、相应的时钟边沿会将数据更改为下一个位。 在 SDI 上、位变化发生在每个时钟上升沿、而在 SDO 上、位变化发生在每个时钟下降沿。 数据由 ADC 在时钟下降沿读取、由主机/MCU 在时钟上升沿读取。

请参阅器件数据表中的时序图(图2)。 RD 脉冲之后的第3个下降沿与 SDO 上的第一个位转换对齐、这意味着 SDO 现在被有效数据驱动。

此致、

Ryan