Other Parts Discussed in Thread: DAC38RF82EVM, DAC39J84, TSW14J57EVM

主题中讨论的其他器件: DAC39J84、 TSW14J57EVM

您好!

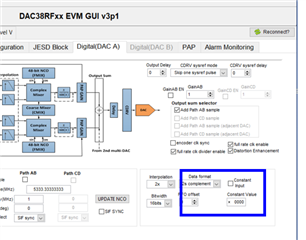

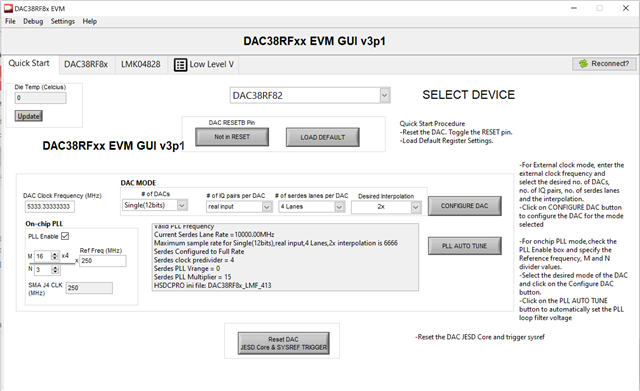

我已经使用 GUI 配置了 DAC38RF82EVM。 我们使用 CMODE3、PLL 频率=250MHz。

DAC 数量=单个(12位)

每个 DAC 的 IQ 对数=实数输入

每个 DAC 的串行器/解串器通道数= 4个通道

所需插值= X2

GUI 快速配置:

"有效的 PLL 频率

当前串行器/解串器通道速率= 10000.00MHz

单通道(12位)、实数输入、4通道、2倍插值的最大采样率为6666

串行器/解串器配置为全速率

串行器/解串器时钟预分频器= 4

串行器/解串器 PLL Vrange = 0

串行器/解串器 PLL 倍频器= 15

HSDCPRO ini 文件:DAC38RF8x_LMF_413"

我们还观察到 PLL LF 电压= 4。

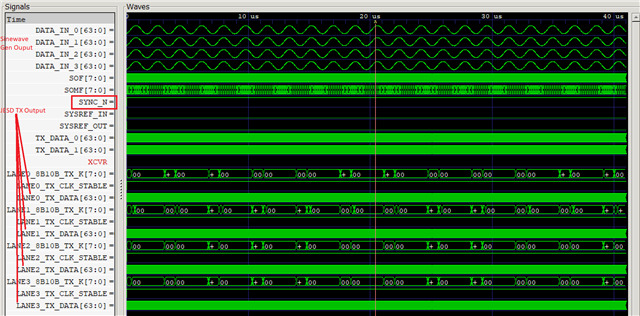

我们观察到、我们已正确接收到来自 DAC38RF82EVM 的 JESD204B RX 的 SYNC0B (高电平)。

我已附上 GUI 配置的 PPT。

我们是否正确配置了 DAC38RF82EVM。 如果您发现任何问题、请检查并告知我们。

谢谢、

Imran