Other Parts Discussed in Thread: ADC124S051

您好!

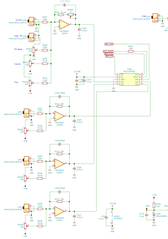

我使用 连接到 FPGA 并以最高8MHz 时钟速率运行的 ADC124S051、以连续循环周期转换4个不同的信号源。 我看到多路复用输入之间存在明显的串扰、在这种情况下、前一转换的结果会影响电流转换。 我已经尝试了许多方法来解决此问题:

1) 1)将采样率从500kSPS 降至375kSPS -没有帮助。

2) 2)在采样采集期间将 SPI 时钟停止几微秒以延长稳定时间-没有帮助。

3)引入长时间的/CS 置为无效(高电平)来分离转换-没有帮助。

4) 4)每通道执行两次连续转换、仅使用第二次结果-第二次结果仍然受到污染。

我发现防止通道间串扰的唯一方法是不更改多路复用器设置-仅连续转换一个输入通道。 这可以防止串扰、但当然不允许我按照系统要求对全部四个通道进行采样。

我直接使用低阻抗运算放大器输出驱动 ADC 输入、并且在引脚附近还有0.01uF 电容器、用作采样过程的电荷库。 我已经通过基准 DMM 测量证实、进入 ADC 的模拟电压不会在外部相互影响。

我是否有任何建议可以解决这个问题?

谢谢、

Eric