我的问题如下:使用 FPGA 与 ads1283通信以收集模拟信号,下载参数后、drdy 和 SCLK 的时序与手册的计时不一致。

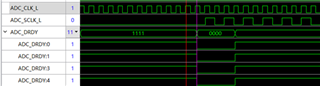

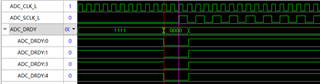

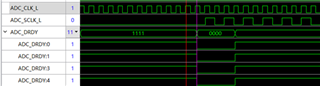

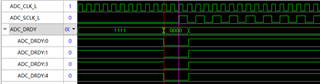

下面的两个图显示了,通常情况下、ddy 信号仅包含一个 SCLK 波形、但在我的计时中、ddy 信号偶尔包含两个 SCLK 波形。 这将导致我收集的数据有时是正确的、有时是小。的两倍

参数:sclk2.048MHZ,clk4.096MHZ

下图包含 CLK、SCLK 和 drdy 信号(右1、错误)的时序

请提供您的建议。

最恰当的考虑

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我的问题如下:使用 FPGA 与 ads1283通信以收集模拟信号,下载参数后、drdy 和 SCLK 的时序与手册的计时不一致。

下面的两个图显示了,通常情况下、ddy 信号仅包含一个 SCLK 波形、但在我的计时中、ddy 信号偶尔包含两个 SCLK 波形。 这将导致我收集的数据有时是正确的、有时是小。的两倍

参数:sclk2.048MHZ,clk4.096MHZ

下图包含 CLK、SCLK 和 drdy 信号(右1、错误)的时序

请提供您的建议。

最恰当的考虑

你好,Lidong,

感谢您提供屏幕截图和时钟信息!

您如何处理应用程序中的/CS 单个? /CS 是否连接低电平、或者/CS 信号是否在/DRDY 信号变为低电平时驱动为低电平?

我提出的原因是/CS 下降沿和第一个 SCLK 上升沿之间需要一段延迟时间。 如果没有这种延迟、接口可能没有足够的时间将 DOUT 驱动至正确的逻辑电平、并且可能会忽略第一个 SCLK。

此致、

Chris