您好!

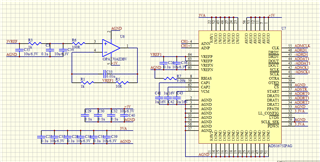

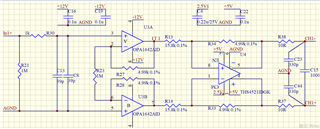

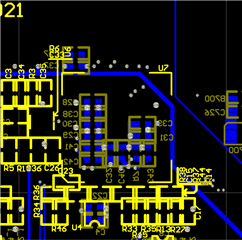

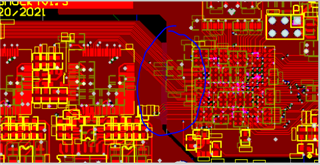

我在宽带宽滤波器模式下使用 ADS1675。 我将 START 引脚设置为高电平以实现连续 SAMP。 我可以看到 DRDY 脉冲、并且输出日期 正确。 但是、当电路板外部存在 EMI 噪声(如空气中的 ESD)时、DRDY 脉冲将会丢失。DRDY 引脚和数据 将保持低电平。 此时,我可以看到 START 引脚保持高电平。 如果我不执行任何操作,此状态将继续。 如果 我将 START PIN 清零,然后设置为 Hige,DRDY 将再次显示,SAMP 数据将再次正确。

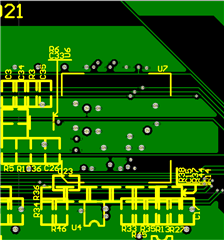

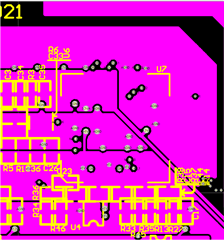

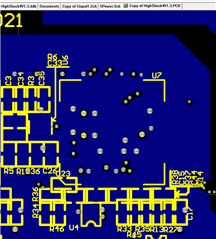

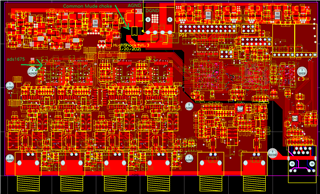

在我的板上还有其他芯片、例如 DSP、FPGA 等、它们始终工作正常。