我有定制硬件。 我们使用的 AFE5809以 60MHz 的频率运行 ADC、并且仅使用一个通道。 我们似乎有很多噪声、但我无法通过引脚指出它的来源。

出于测试目的、我将输入短接至 GND 并通过 FPGA 读取 ADC。 我看起来 随机噪声的峰值 高达+/- 80十进制。

我们的 LNA 配置为24dB 增益、PGA 配置为30dB 增益、总计54dB。 我们是否应该看到低于该值的数字?

下面是我们的原理图中显示输入的一个小工具:

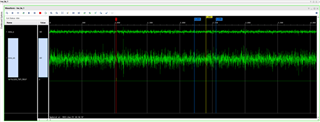

这是 FPGA 读出的一个小插曲

我尝试禁用了电路板上的模拟 VCNTL、并且仅使用具有0dB 衰减的数字 VCAT -结果相同。

已尝试50R 内部端接、也已禁用内部端接-结果相同。

我还应该寻找什么?

顺便说一下、内部基准电压的幅度是多少? 在数据表中、REFM 和 REFP 分别表示为0.5V 和1.5V。 这是否意味着基准电压为1.0V?