Other Parts Discussed in Thread: ADS1672

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADS1672 大家好、

我们从客户处获得以下信息。

- CLK 的占空比

如果发生多次转换、客户将配置 ADS1672 CLK = 20MHz、FastResponse、LowLatency、DR=625kSPS。

根据数据表、CLK 的占空比应非常接近50%、而时序要求中的最小值、最大值显示45%和55%。

它是否足够最小45%和55%? 如果没有,可以共享目标号码吗? - 时钟抖动的目标数

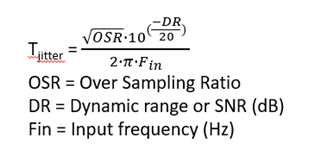

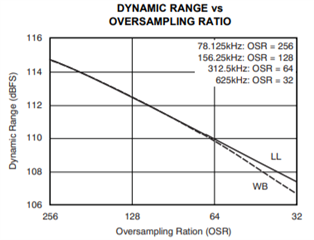

如果配置 CLK=20MHz、FastResponse、低延迟、DR=625kSPS、并且在600Hz 至60kHz 之间实现最大 SNR、客户希望知道时钟抖动的目标数量。

或者、如果我们可以分享图2等数字、那会很有帮助。 过采样 ADC (A)或表1等数据的 SNR 图。 显示时钟抖动、SNR 和频率之间的关系。 您能否共享这些数据以实现时钟抖动? 客户担心由于增加抖动而降低 SNR 性能。

谢谢、此致、

米希亚基