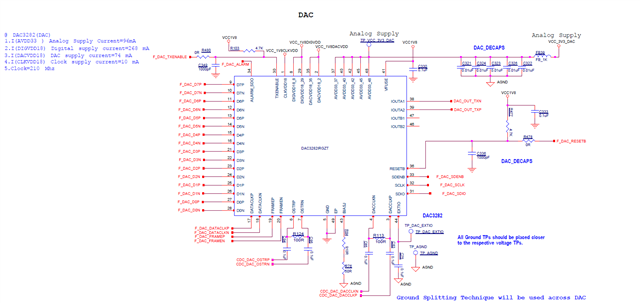

Other Parts Discussed in Thread: DAC3282, DAC3283

主题中讨论的其他器件: DAC3283

您好 TI 团队

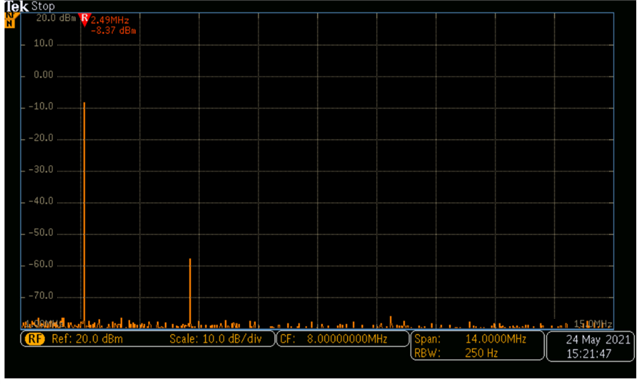

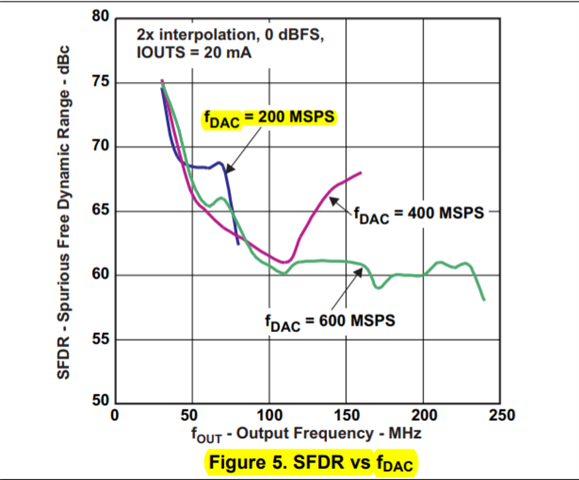

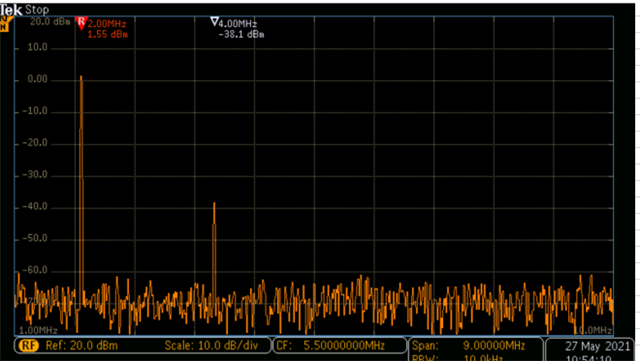

在 DAC3282的输出端、我们将得到2次和3次谐波。 随着我们在后一级使用放大器、这些谐波在发送器链中得到放大。

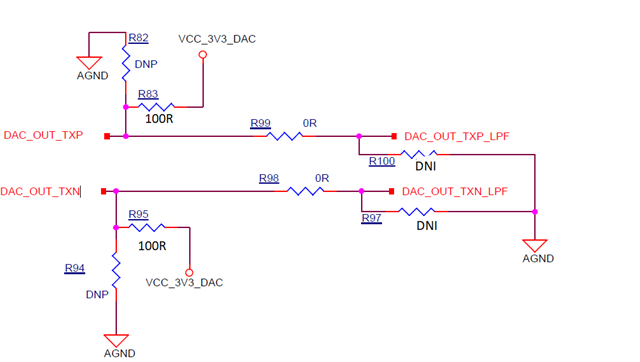

我们的信号带宽为500kHz - 20Mhz、DAC 采样率为210MSPS (使用 x2插值)。 DAC 增益为 X66。 在后续阶段、我们将使用 LPF 截止28Mhz。

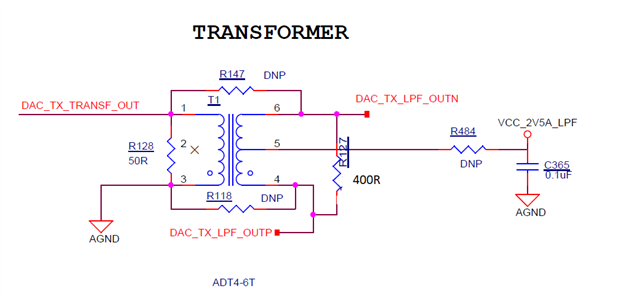

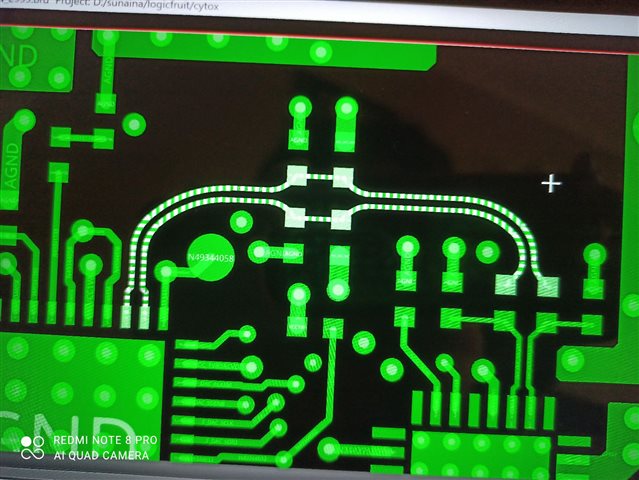

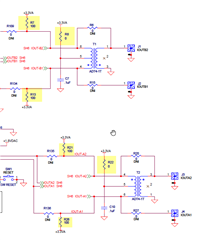

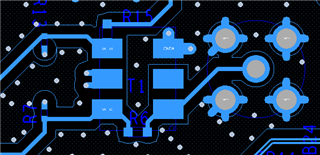

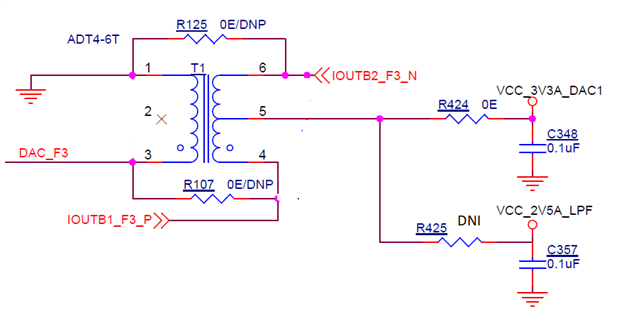

DAC3282和 DAC 前端电路的 PFB 原理图。 DAC CLK 为 LVPECL 210MHz。

请建议审核点以尽早解决此问题。

此致

Balvan Singh