请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADS1278 尊敬的 TI 社区:

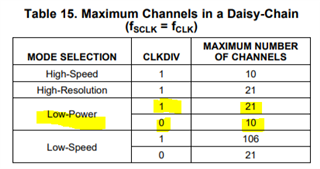

我想知道、当 ADS1278设置为低功耗模式时、是否存在差异、与数据速率和过采样频率的部分、如果我将 CLKDIV 设置为1或0。

在我的应用中、我只需要获得2kSPS。 为此、我为 Fclk 使用2.048MHz 振荡器。

在我看来、最好将 CLKDIV 设置为0、以获得可能的最高数据速率(Fdata)和最高过采样频率(Fmod)。

是否有理由我宁愿将 CLKDIV 设置为1 (例如消耗)?

感谢您的帮助!