请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADC12DJ5200RF 我正在使用 ADC12DJ5200RF 设计电路板。

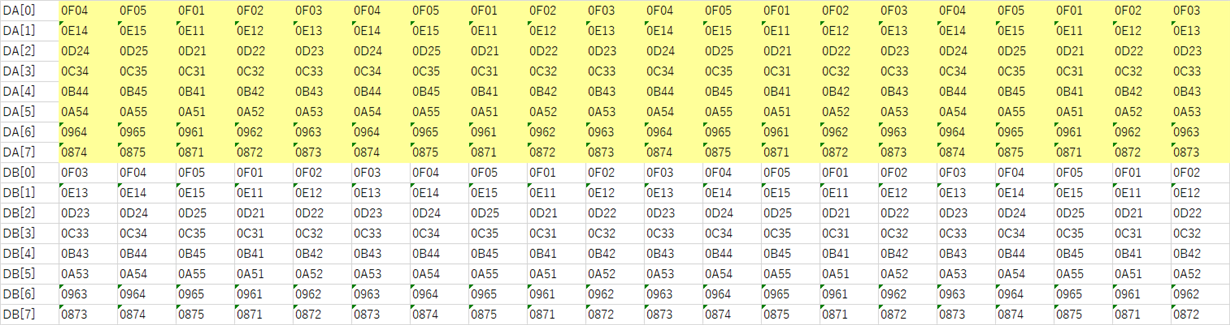

当我使用 JMODE1将测试数据从 ADC 发送到 FPGA 时、我注意到数据有时在 DA 的8个通道和 DB 的8个通道之间偏离。

(如果 FPGA 正确接收数据、我认为 DA [x]= DB [x]、但它没有。)

是否可以通过在 FPGA 侧设置某个内容或在 ADC 侧设置某个内容来解决该问题?