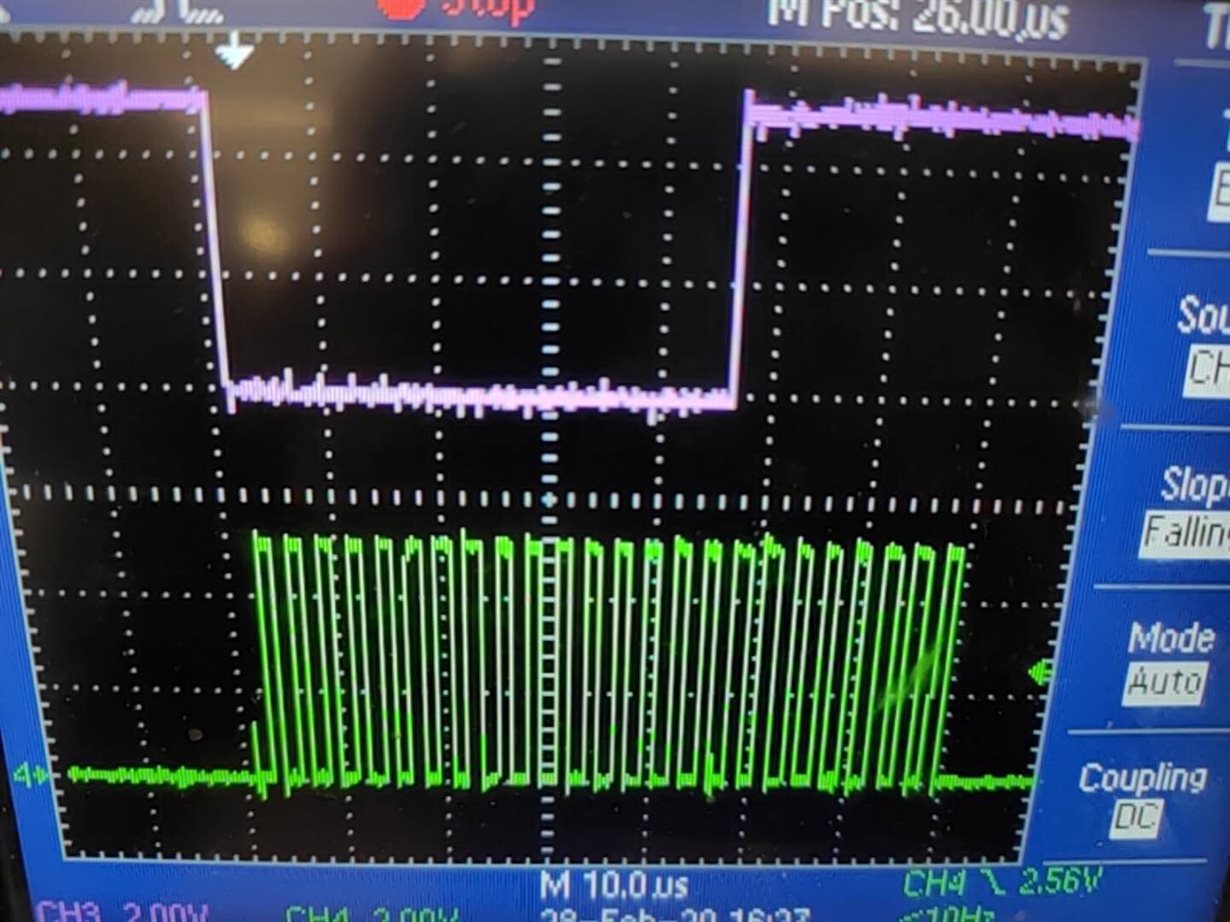

我的代码不起作用,问题出在哪?

void DAC2_set (U16值)

{

字符 I;

DAC_CS1_L;

for (i=8;i>0;i--)

{

DAC_DIN_L;

DELAY_us (1);

DAC_SCLK_H;

DELAY_us (1);

DAC_SCLK_L;

}

for (i=16;i>0;i--)

{

if (值0x8000)

{

DAC_DIN_H;

DELAY_us (1);

}

其他

{

DAC_DIN_L;

DELAY_us (1);

}

DAC_SCLK_H;

DELAY_us (1);

DAC_SCLK_L;

值<<= 1;

}

DAC_CS1_H;

}