主题中讨论的其他器件: LM3409

您好!

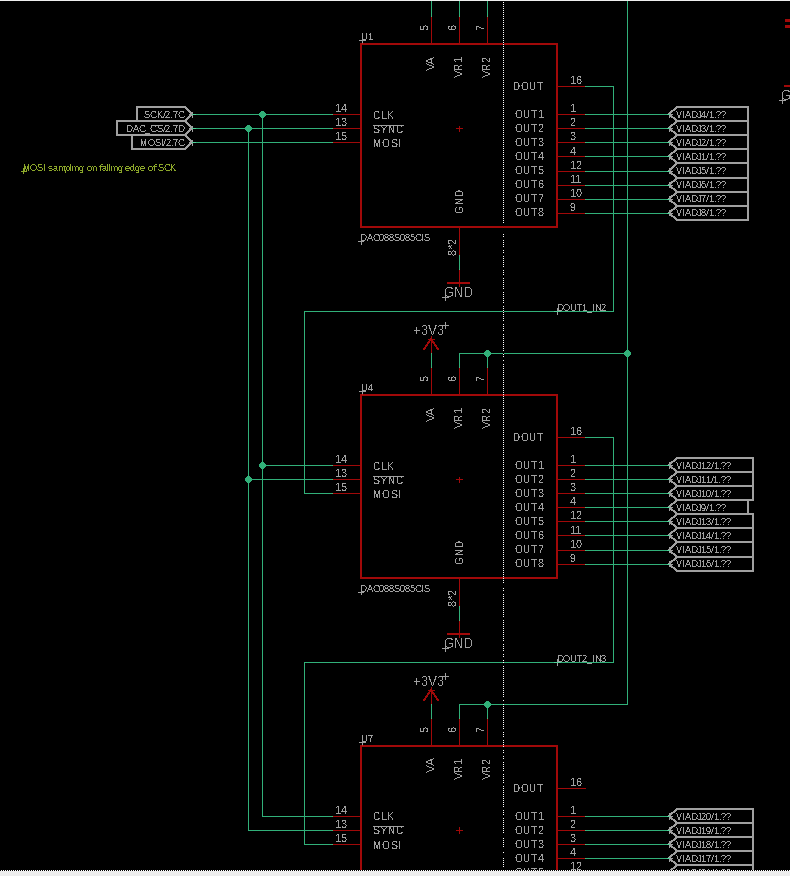

我尝试使3个 DAC088S085在菊花链模式下工作。

我能够使前2个 IC 使用良好的模拟输出、但第三个 IC 即使在 WRM 或 WTM 中也不工作。

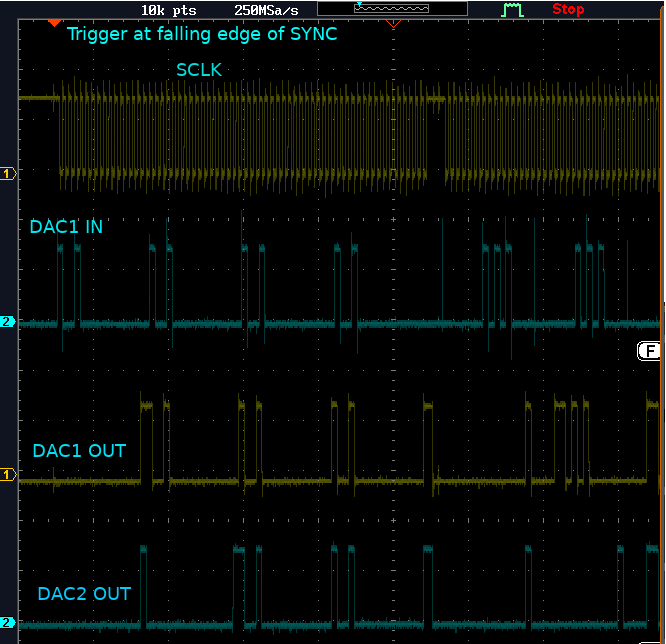

在示波器上、我可以看到、在第一个 IC DIN 和 DOUT 相位差大约90°。 以下是我的测量值:

顶部通道是来自 MOSI 的输入、第二个是 SCLK、第三个是 IC 的 DOUT。 这是正常的吗?

因此、第一个 IC 在 SCLK 的下降沿对数据进行采样、而其他 IC (第二个和第三个)在上升沿进行采样。

我尝试更换所有 IC、检查焊接(这些是 WQFN 封装)。 我尝试移除 IC #2和#3、但结果相同。

有什么想法吗? 谢谢。

塞尔日