大家好、团队、

您能帮助我们解决 DPOT 设置问题吗?

输出不会线性变化。

在我的用例中、SCLK = 5MHz、DPOT 值在200kHz 频率下按顺序更新。

在错误的设置中、LSB 不正确。 当递增 DPOT 值时、输出有时会上升或下降。

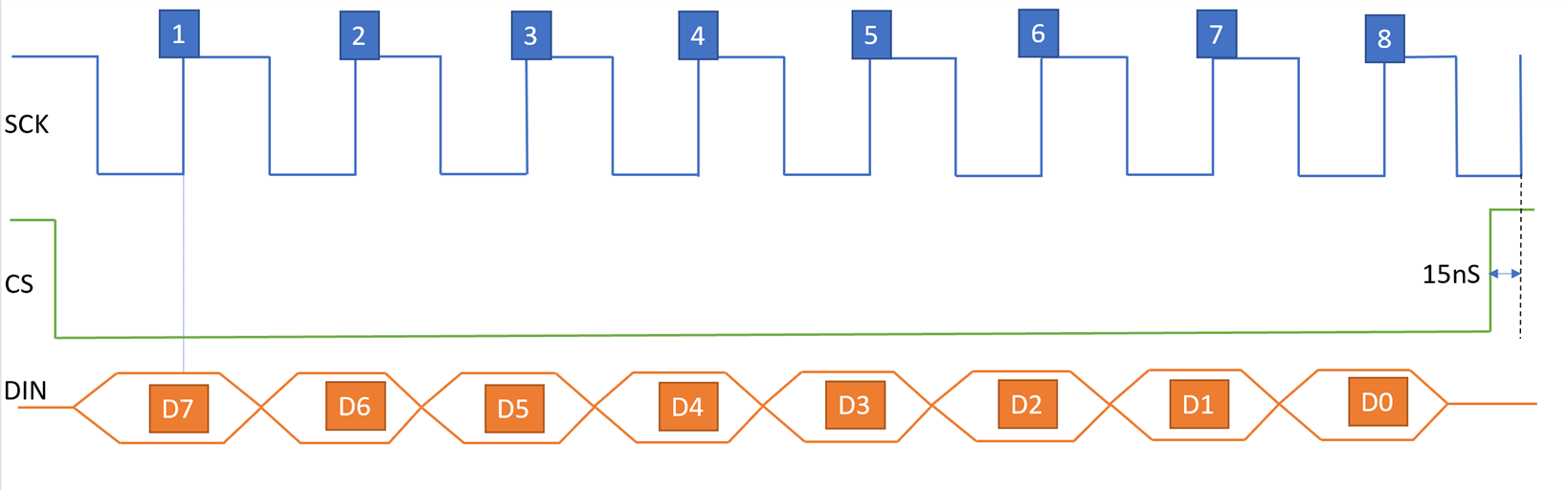

发生此问题时、SPI 时序看起来有点可疑。

在 D/S 图16中、显示了 t_CS1。 当问题发生时、T_CS1变为负(意味着当 SCLK=H 时 CS 上升沿生效)。

请注意、tcsh 有1个时钟持续时间。

第一。 在 D/S 中、未指定 t_CS1要求。 t_CS1或其他时序是否有任何限制? 我需要注意什么?

2。 当 T_CS1变为负值时、看起来 SPI 禁用失败、因为在该事件发生后、输出会反映 CS=H 下的 SDI 输入

我假设在确认正确的 T_CSS 时启用 DPOT。

另一方面、您能否告诉我何时需要禁用 DPOT?

3号。 您能否告诉我以200kHz 频率更新 DPOT 的注意事项?

您建议执行什么调试操作?

此致、

Itoh