Other Parts Discussed in Thread: DAC108S085, TMS320F280049

主题中讨论的其他器件: TMS320F280049

您好,

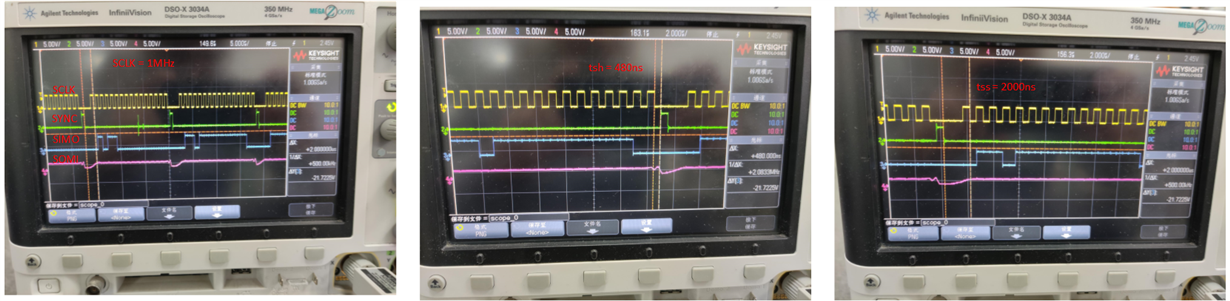

我的 DAC108S085有问题。 说明手册说 TSS 的最小值为3-10ns、最大值为(1/fSCLK - 3)。 我使用 TMS320F280049将这个 DAC 模块化连接、但是它的 TSS 输出参数不能满足 DAC 芯片的要求。

那么、我有两个问题、

1. TSS 值是否应在上述范围内

2.是否可以更改 TMS320F280049的 TSS 值? 我找不到要配置的方法。

希望答复。

谢谢