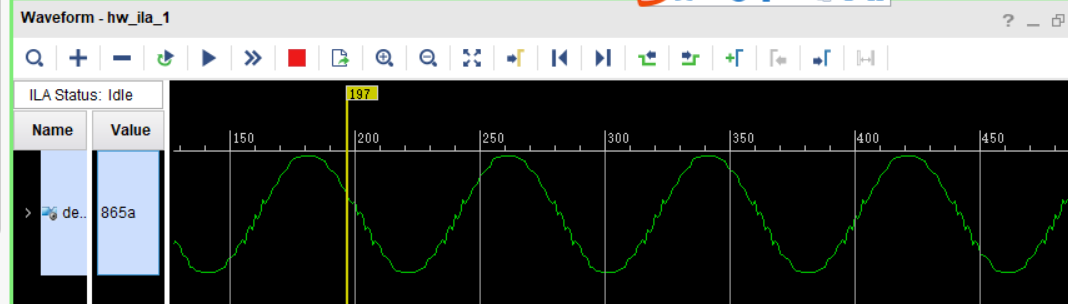

目前、Xilinx 的 FPGA 用于 ads5560采集方案、并且收集的正弦波数据存在失真问题。

当 ads5560配置为测试模式时、规范中提到的数据和数据模式完全对应于无错误模式。

在全0测试模式下、FPGA 接收的16位 AD 数据始终为0

在所有1s 测试模式下、FPGA 接收的16位 AD 数据始终为1

在切换模式测试模式下、FPGA 接收的16位数据也将是0x5555到0xaaaa。

在斜坡 Peter 测试模式下、fgap 接收到的16位数据为0x0000到+ 1到0xFFFF。

上述四种测试模式均为0位误差、因此认为 FPGA 通过 AD 传输的1 LVDS 时钟和8 LVDS 数据信号在信号质量和内部采集时序方面没有问题。

在确定 ads5560和 FPGA 之间的数字传输误差为零的条件下、哪些因素可能会导致 ads5560在工作模式下的波形失真? 就所收集的数据而言、它与模拟电路的最低噪声不同。 使 ads5560的模数转换成为数据输出的 ads5560的芯片配置问题还是模拟电路的硬件设计问题是否存在问题?

毕竟、电流测试可以考虑 ads5560的数字引脚上的值以及 FPGA 确切收集的值。 因为所有四种数字测试模式都可以无误地通过。

模拟端口的波形可由示波器测量。 即使电路具有底部噪声、模拟电路的连续性也不应导致 AD 数字终端的数据故障类型突变。

目前、Xilinx 的 FPGA 用于 ads5560采集方案、并且收集的正弦波数据存在失真问题。

当 ads5560配置为测试模式时、规范中提到的数据和数据模式完全对应于无错误模式。

在全0测试模式下、FPGA 接收的16位 AD 数据始终为0

在所有1s 测试模式下、FPGA 接收的16位 AD 数据始终为1

在切换模式测试模式下、FPGA 接收的16位数据也将是0x5555到0xaaaa。

在斜坡 Peter 测试模式下、fgap 接收到的16位数据为0x0000到+ 1到0xFFFF。

上述四种测试模式均为0位误差、因此认为 FPGA 通过 AD 传输的1 LVDS 时钟和8 LVDS 数据信号在信号质量和内部采集时序方面没有问题。

在确定 ads5560和 FPGA 之间的数字传输误差为零的条件下、哪些因素可能会导致 ads5560在工作模式下的波形失真? 就所收集的数据而言、它与模拟电路的最低噪声不同。 使 ads5560的模数转换成为数据输出的 ads5560的芯片配置问题还是模拟电路的硬件设计问题是否存在问题?

毕竟、电流测试可以考虑 ads5560的数字引脚上的值以及 FPGA 确切收集的值。 因为所有四种数字测试模式都可以无误地通过。

模拟端口的波形可由示波器测量。 即使电路具有底部噪声、模拟电路的连续性也不应导致 AD 数字终端的数据故障类型突变。