大家好、我正在评估 DAC38RF80EVM、并在它连接到 TSW14J56修订版板时发现了一些问题。

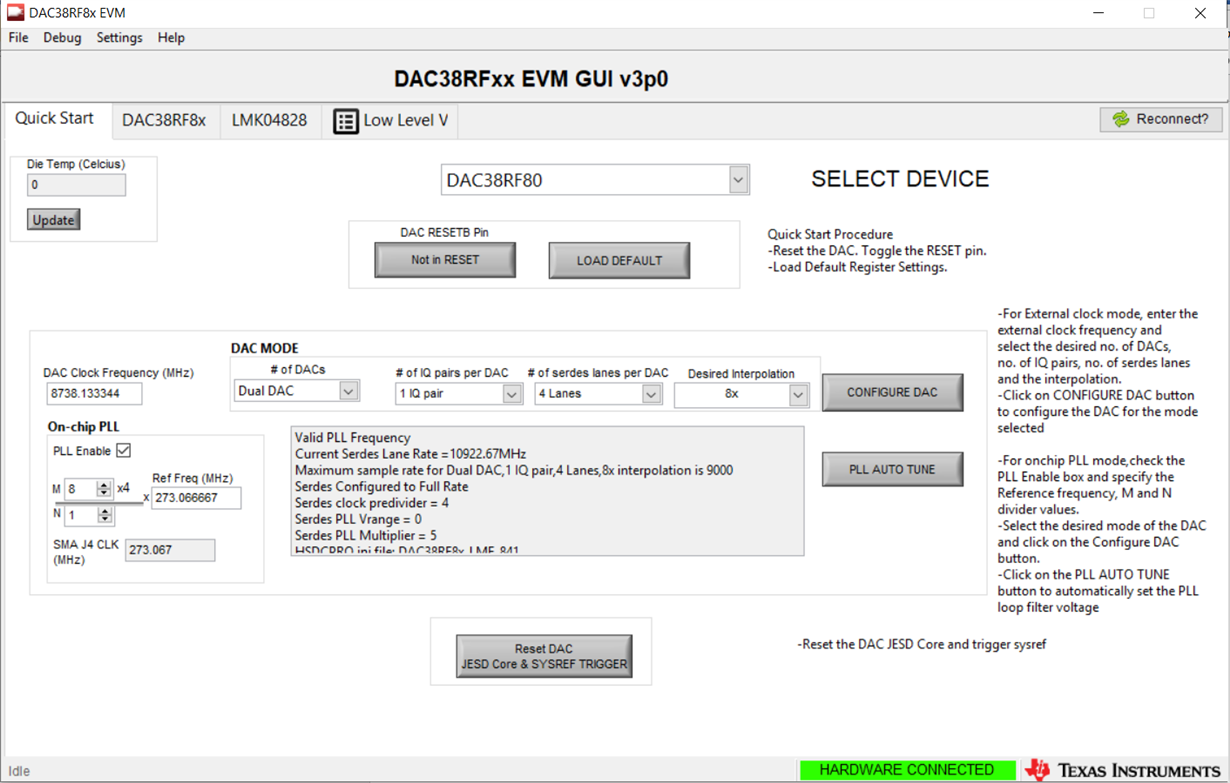

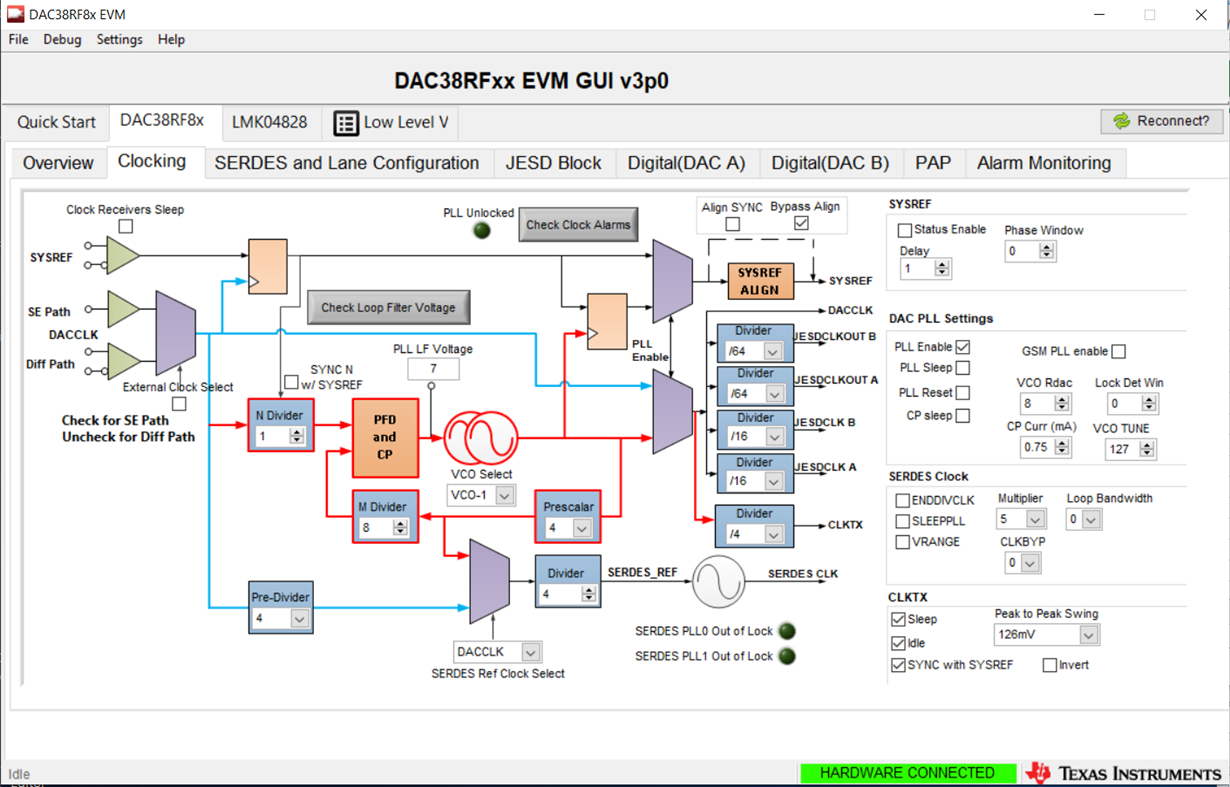

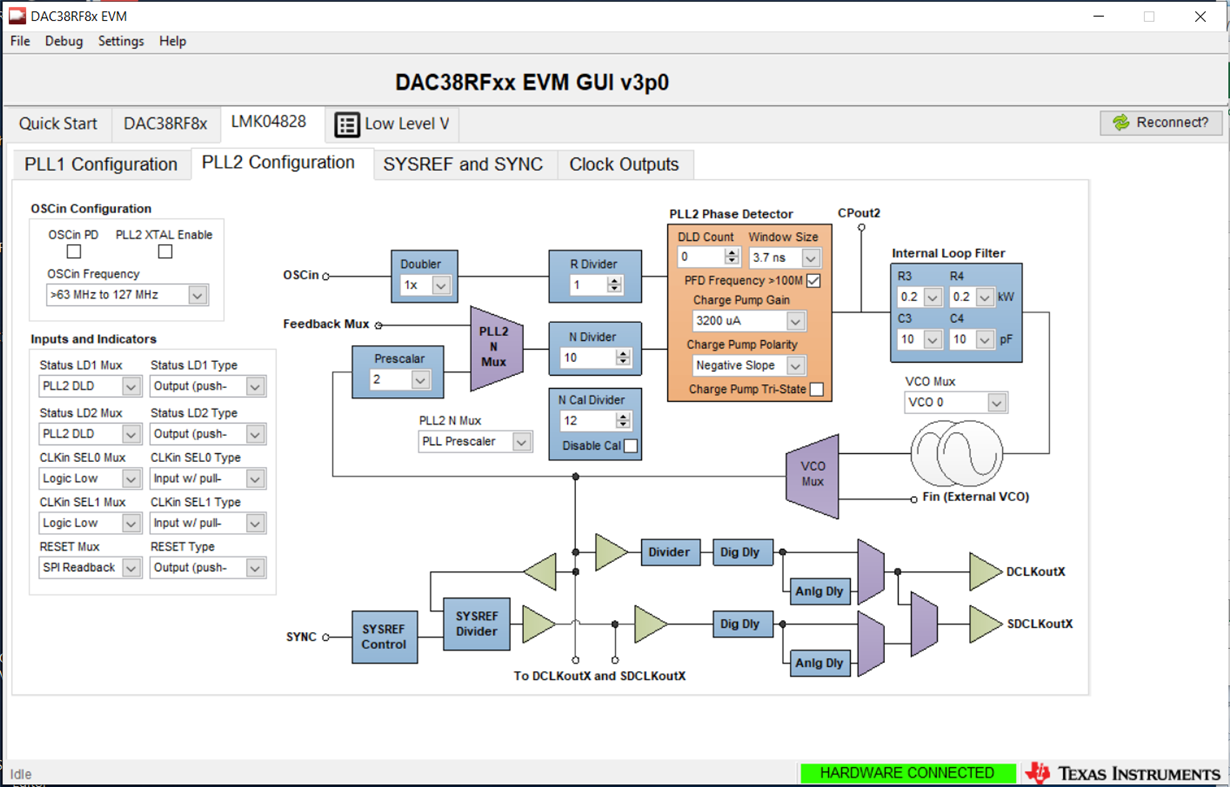

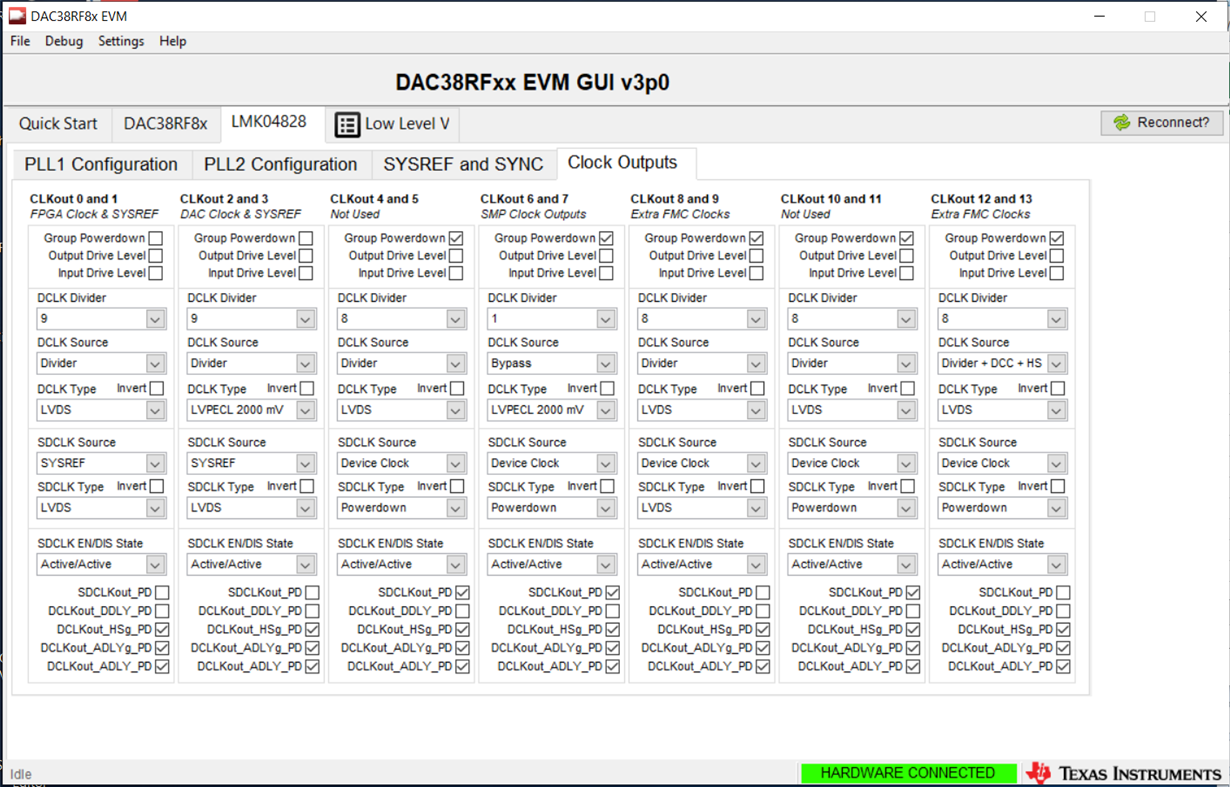

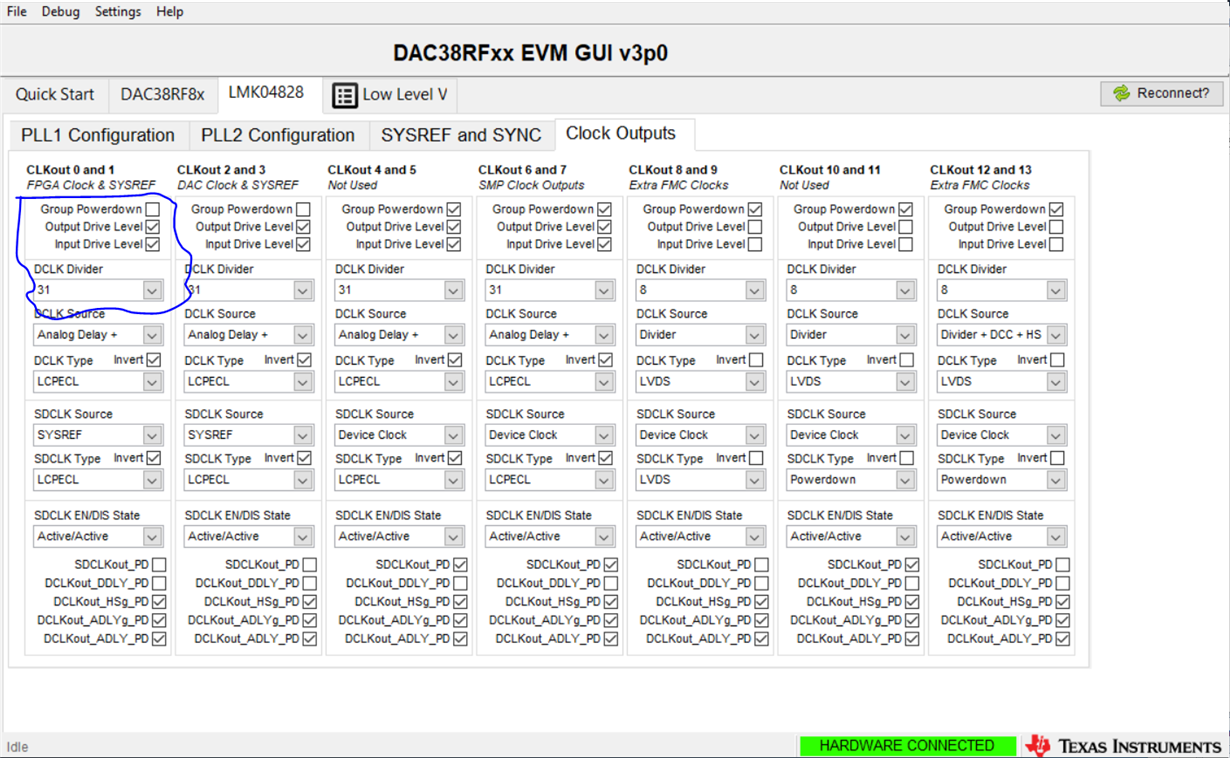

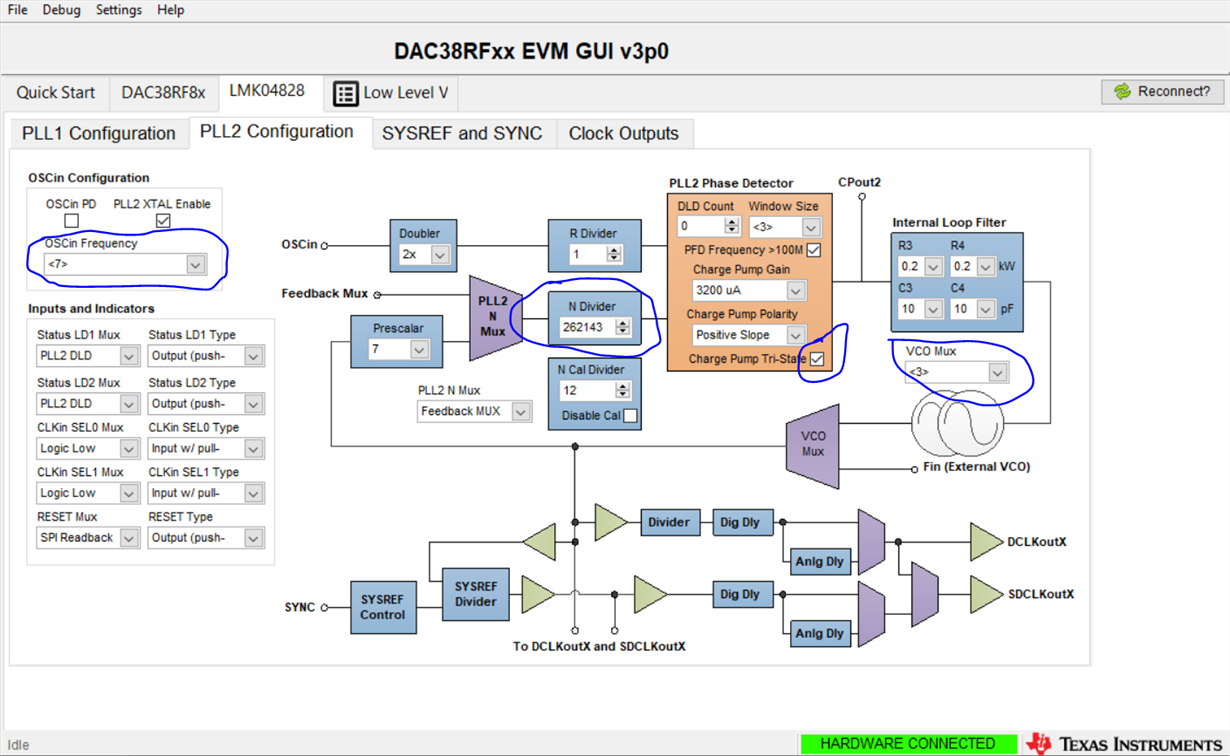

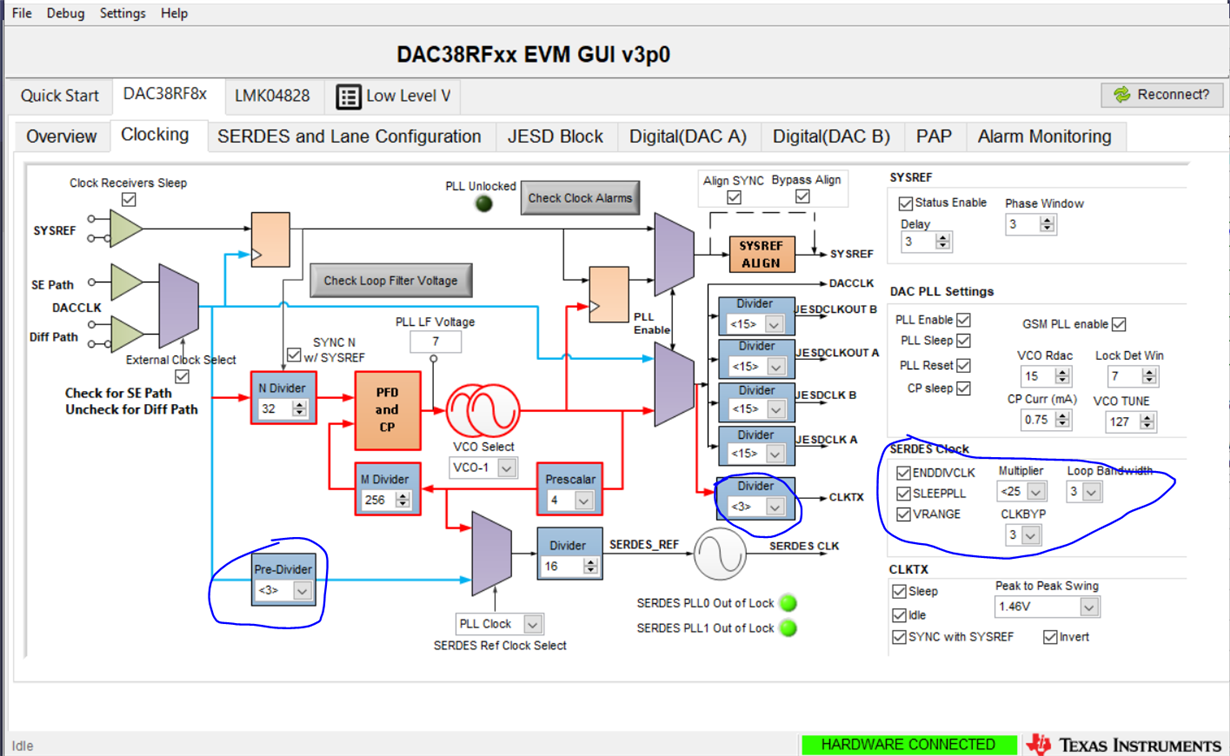

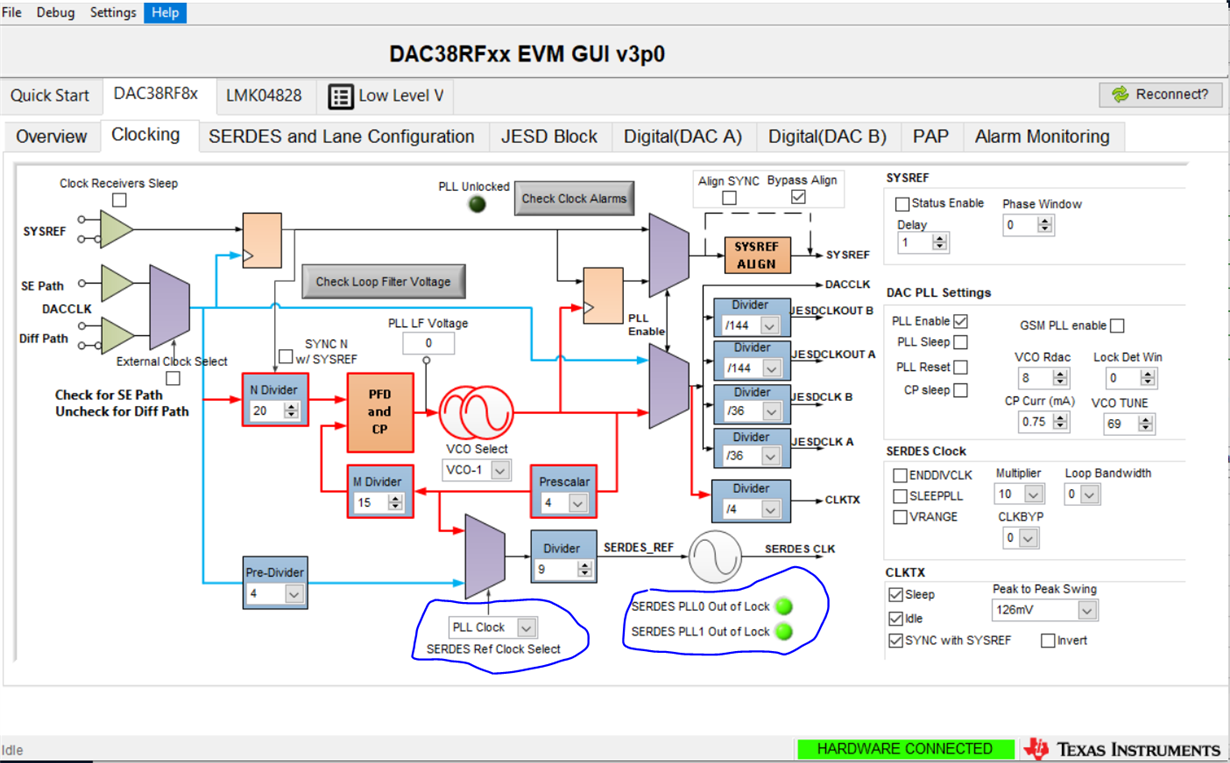

我的当前配置是:使用板载122.88MHz 振荡器作为 LMK 的基准、然后将 LMK 输出用作 DACCLK 和 FPGA CLK。 为了使其正常工作、I DNI C333和 C334并根据原理图安装 C2和 C3。 通过这种修改、我可以看到 LMK 时钟输出进入 DAC、并在 FPGA 板关闭时锁定 DAC PLL。 GUI 配置如下所示:

在没有 FPGA 板的情况下、我可以通过 GUI 控制 DAC 和 LMK 的寄存器、这样就可以使用恒定数据模式成功获得正确的 DAC 输出。

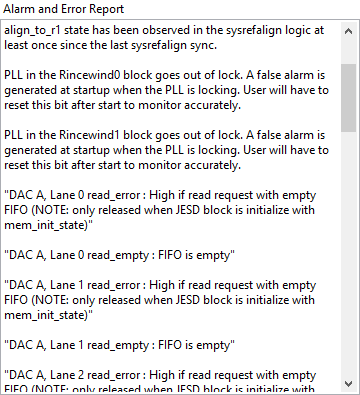

但是,打开 TSW14J56revD FPGA 板后,便无法通过 GUI 修改 DAC 评估板的寄存器。 例如、我将 LMK DCLK 分频器设置为9、它回读为31。 我无法更改 LMK 的 N 分频器、并且 CP 三态始终开启。 VCO 选择不可用。 不提供"其他"选项。 我无法在计时选项卡中设置 DAC 寄存器。 因此、DAC PLL 显示为未锁定。

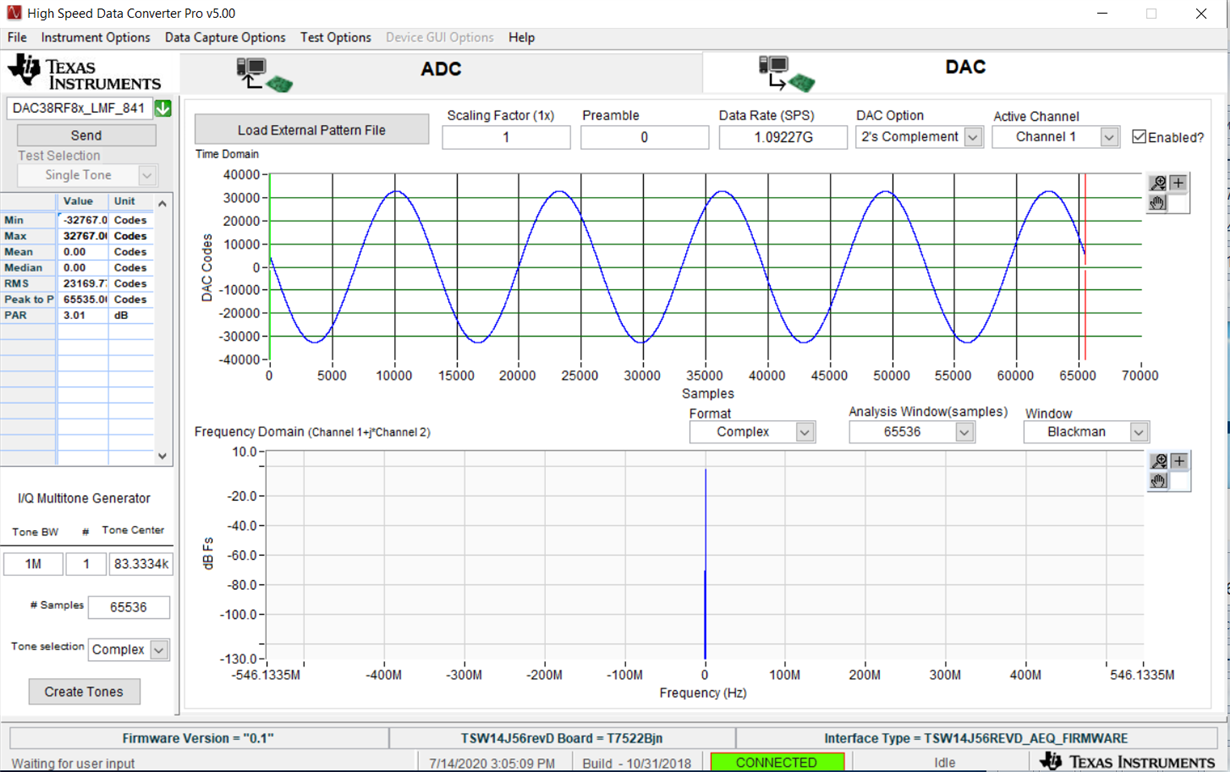

然后、我尝试从 FPGA 板创建图形并发送到 DAC 板:

我收到此警告:JESD REF CLK 需要为237.0665MHz。

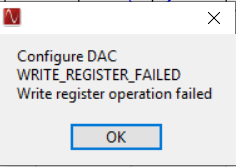

然后、我收到以下错误消息:WRITE_REGISTER_FAILED

我有以下问题:

1)这是将板载122.88MHz osc 用作 LMK 基准、将 LMK 输出用作 DACCLK 和 FPGA CLK 的正确配置。

2) 2)频率配置对于 LMK 和 DAC 而言是否有道理获得正确的 DACCLK、FPGA CLK、JESD 基准时钟? 我是否会始终收到有关 JESD 基准时钟的第一条警告消息?

3) 3)为什么 FPGA 板会不断复位寄存器? 我尝试了两个 revD 板、观察到了同样的情况。

感谢您的支持。