主题中讨论的其他器件: ADS54J64、 LMK04828

您好!

我的客户计划通过 FMC 连接器将 ADS54J64EVM 连接到其 FPGA 板。

实际上、他们尝试在没有 TSW14J56EVM 或 FPGA 板的情况下自行运行 ADS54J64EVM。

根据《ADS54J64评估模块用户指南》2.3.1,他们按照以下步骤#1至#3操作。

1.从开始菜单→所有程序→德州仪器→中打开 ADS54J64EVM GUI

ADS54J64 EVM。

2. GUI 启动后,验证 GUI 右上角的绿色 USB Status 指示灯是否亮起

照明。

3.在简介选项卡中、按下标有"Fclk=983.04MHz"的配置 LMK04828按钮。

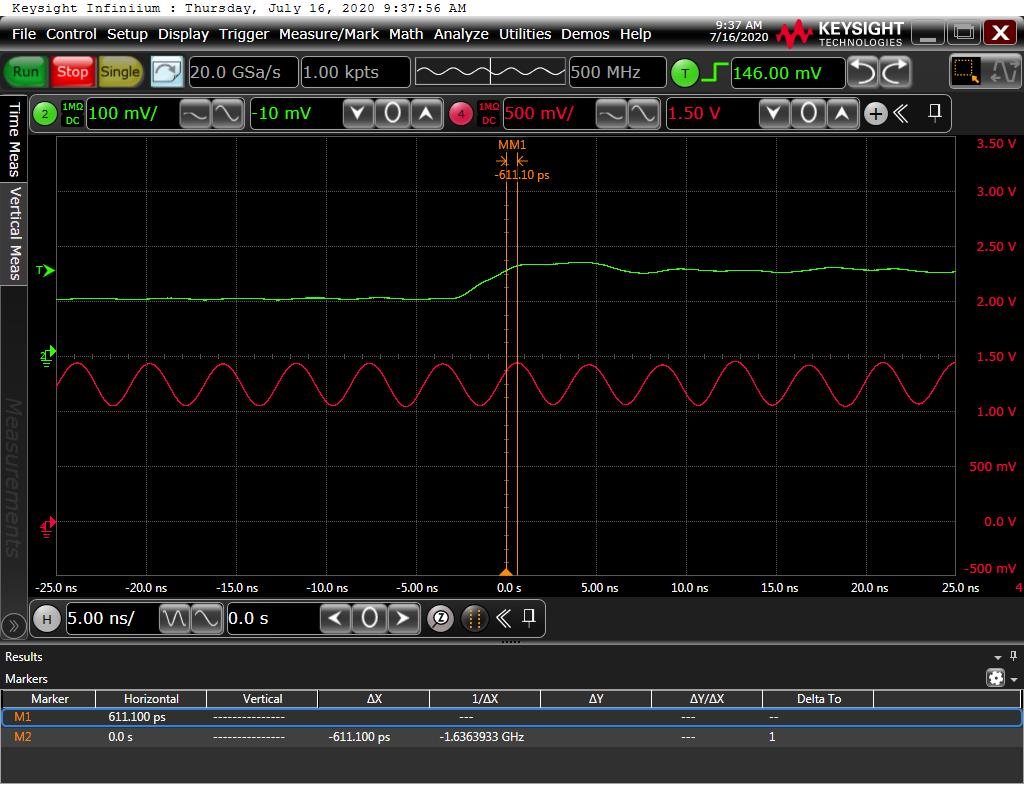

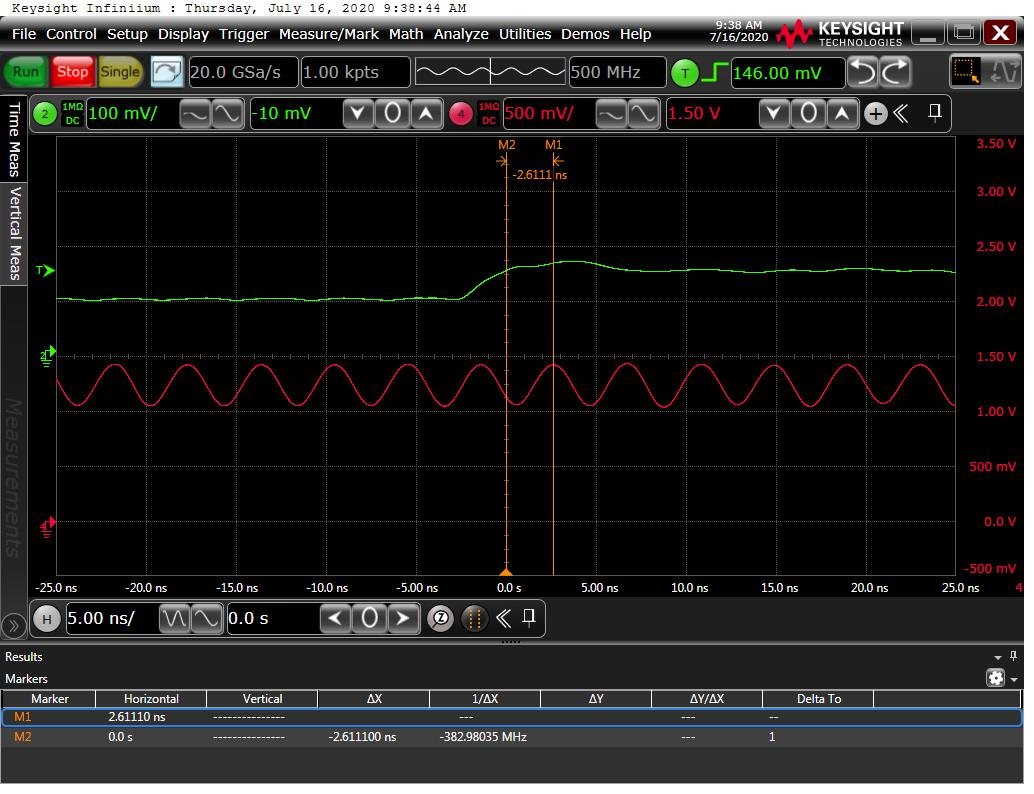

之后、它们通过示波器观察到 DCLKOUT0 (器件时钟)和 SDCLKOUT1 (sysref)。

它们之间的相位关系在每个下电上电周期中都是不同的。

他们期望它们之间具有固定的恒定相位关系、因为它们是 JESD 器件时钟和 sysref。

为什么它们的相位关系不是确定性的? 出什么问题了?

为了获得之间的确定性相位关系、我的客户需要做什么?

此致、

希拉诺