各位同事、

您能帮助解决我的客户提出的输出数据速率问题吗? 他正在使用 ADS131E08。

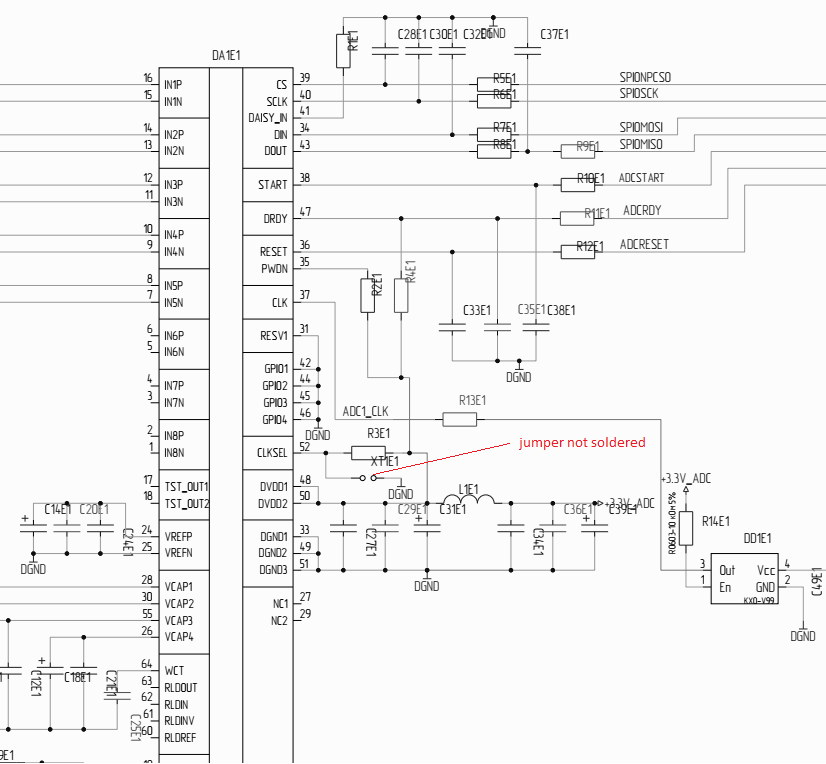

内部时钟为2.048MHz。 客户尝试设置不同的 DR CONFIG1设置、但始终获得比应有低两倍的数据速率和/DRDY 信号。

例如、他使用值101、而不是2kHz、他得到的是1kHz。

他还检查了寄存器的值、并正确设置了这些值。 他还尝试使用差分 SPI 时钟(6、10、20MHz)、但每次 DRDY 信号的值都有两个限制。

您能告诉我他应该检查什么吗? 或者、这里可能会出现什么问题?

谢谢、Mikhail