主题中讨论的其他器件: LMK04826

你(们)好

我们遇到了 DAC38J84问题。

FPGA -- Virtex 7.

时钟发生器 -- LMK04826

DAC DAC38J84

在 DAC34J84中、有一些错误/警报指示

a. 8b/10b 视差误差

b. 8b/10b 不在表代码中错误

c.代码同步错误

d.弹性缓冲区溢出错误

e.链路配置错误

f. 帧对齐错误

g.多帧对齐错误

h. FIFO 已满

i. FIFO 为空

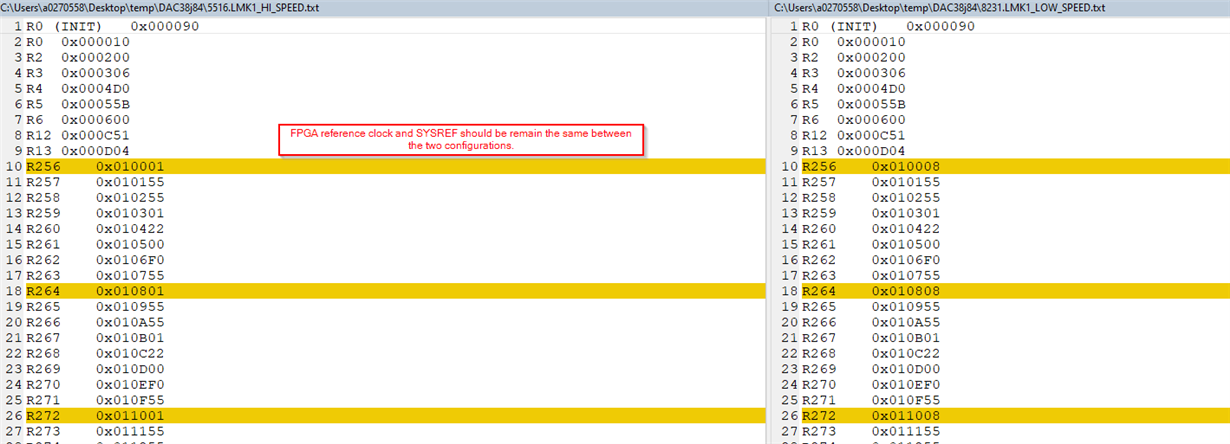

我们将 DAC 配置为两种模式

低速312.5MSPS 采样率下。

2.高速2.5GSPS 采样率。

案例1:低速

串行器/解串器速率 = 6.25Gbps

LMK 时钟频率至 FPGA = 156.25MHz (SERDES 速率/ 40)

将 LMK 时钟频率更改为 DAC = 312.50MHz

SYSREF 频率 = 4.8828125MHz (FPGA 时钟/ 64)

内插 = x 1

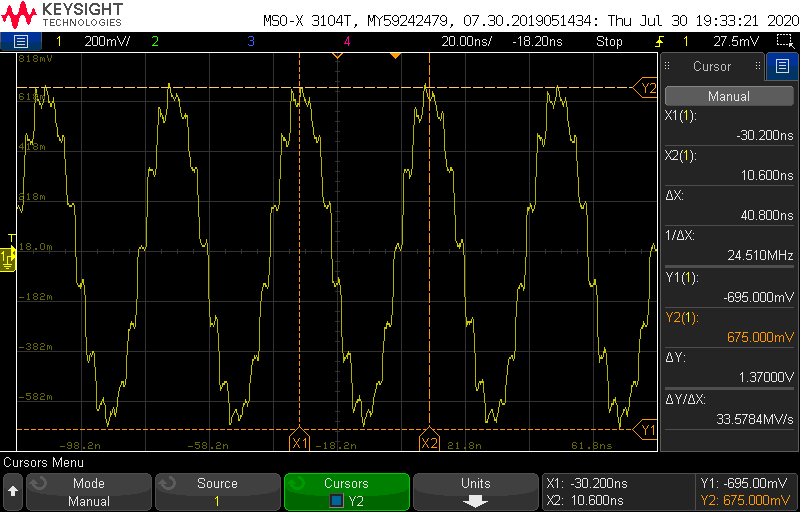

DAC 的输出数据 =单个25MHz

我们将测量进入 FPGA 和 DAC 的时钟。 它们符合规格。

在低速下、我们能够从 DAC 捕获正确的数据。

JESD 链路已建立、DAC 中没有警报。

案例2:高速

串行器/解串器速率 = 6.25Gbps

LMK 时钟频率至 FPGA = 156.25MHz (SERDES 速率/ 40)

LMK 时钟频率至 DAC = 2.5GHz

SYSREF 频率 = 4.8828125MHz (FPGA 时钟/ 64)

内插 = x 8

DAC 的输出数据 =单个25MHz

我们将测量进入 FPGA 和 DAC 的时钟。 它们符合规格。

高速时、我们无法从 DAC 捕获正确的数据。

JESD 同步信号持续切换、DAC 中存在警报。

我们将在高速下获得以下警报/错误指示

a. 8b/10b 视差误差

b. 8b/10b 不在表代码中错误

c.代码同步错误

d.弹性缓冲区溢出错误

E.帧对齐错误

f.多帧对齐错误

g. FIFO 已满

h. FIFO 为空

这些错误表明高速 JESD 链路存在问题。

如果您指导我们解决此问题、将会有所帮助

请查找附件:

低速和高速时的 LMK 配置文件

2.低速和高速 DAC 配置文件

低速 DAC 输出

e2e.ti.com/.../8231.LMK1_5F00_LOW_5F00_SPEED.txt

e2e.ti.com/.../5516.LMK1_5F00_HI_5F00_SPEED.txt

e2e.ti.com/.../DAC_5F00_configurations_5F00_Low_5F00_speed.txt

e2e.ti.com/.../DAC_5F00_configurations_5F00_High_5F00_speed.txt

谢谢你