数据表显示输出电压以 AGD-OUT 为基准(数据表第4页)。 但根据输出电压公式(数据表第23页)、电压以 VREFN 为基准。 DAC11001A 中 AGD-OUT 的内部连接如何? 您能否提供简化版原理图?

是否可以使用运算放大器驱动 AGND 输出?

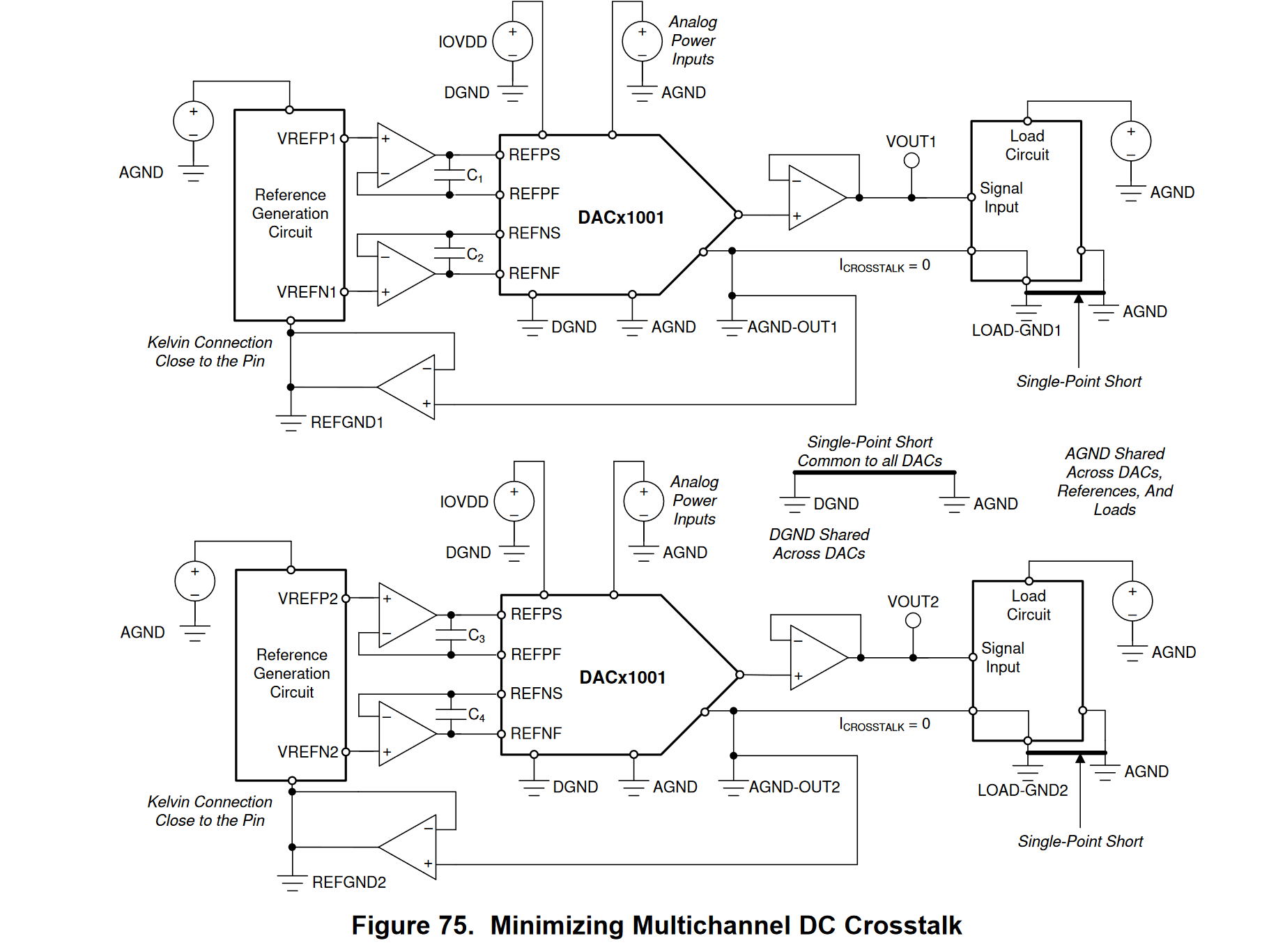

我有一个具有一个基准的多通道系统(VREFP=7V、VREFN=0V)。 根据数据表、输出电压以 AGND-OUT 为基准、但 AGND-OUT 应与 VREFN 具有相同的电位。

其思路是使用运算放大器缓冲 VREFN 电压、并在每个 DAC 上驱动 AGND 输出以防止交叉点。

感谢你的帮助。