主题中讨论的其他器件:DAC8551、 DAC8550

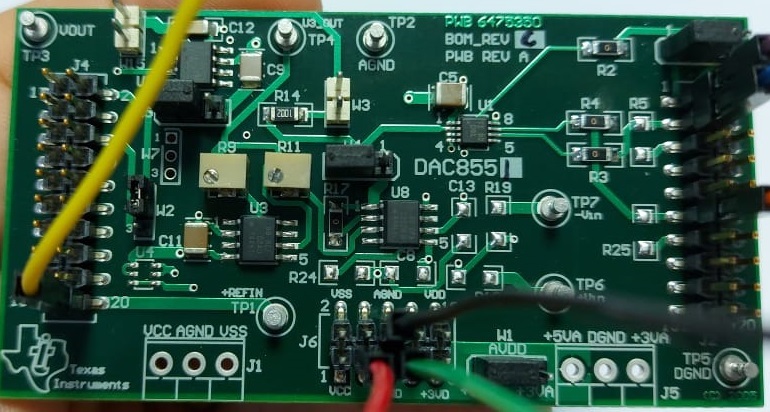

我将 DAC8551评估模块与 TC-399评估套件连接以驱动模拟电压、并按 如下方式连接了 DAC8551评估模块引脚:

- 电源电压:

- J6-3:+5V (Vdd)

- J6-5:GND

- J6-6:GND

- J4-20:+5V (Vref)

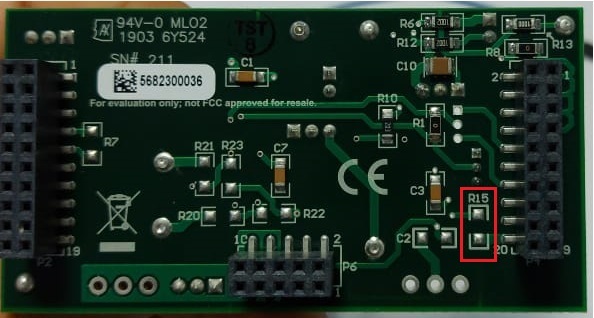

- 跳线设置功能连接:

- W1:为 AVDD 选择+5V 模拟电源。

- W2:(1-2)将 VOUTA 路由至 J4-2。

- W3:(未连接) 断开 VREFH 与输出运算放大器 U2的反相输入

- W4:(3-2)将用户提供的基准从 U4 (如果已安装)、TP1或 J4-20路由到 DAC8550/51/52的 VREFH 输入。

- W5:(1-2)输出运算放大器 U2的负电源轨由 VSS 供电以实现双极运行。

- W6: 来自 J2-1的(1-2) CS 信号被路由以驱动 DAC8550/51/52的 SYNC 信号。

- W7:(未找到) 这是安装 R1时 DAC8550/51EVM 的默认跳线位置。

- W15: (未连接)断开输出运算放大器 U2的反相输入与增益电阻 R12的连接。

- 串行接头连接:

- J2-1:MCU 的 QSPI_CS。

- J2-3: MCU 的 QSPI_SCLK。

- J2-11: MCU 的 MTSR (SDI)。

完成此连接后、我运行软件并发送 Din = 32768以获取 Vout =+5V、但 Vout 仍然等于零、并且我尝试了许多 DIN 和 Vout 值仍然为零。

我希望从 J4-2引脚输出。

请告诉我在连接或使用 评估模块时是否有故障、并帮助我操作评估模块以获得所需的输出电压。

注意:(我没有使用运算放大器、因此我希望 J4-2引脚的 Vout 在使用运算放大器之前获得 DAC 输出、此外、我也没有连接运算放大器的 VCC 和 VSS、因为我希望在 DAC 转换之后输出)