主题中讨论的其他器件:、 ADC08D1500

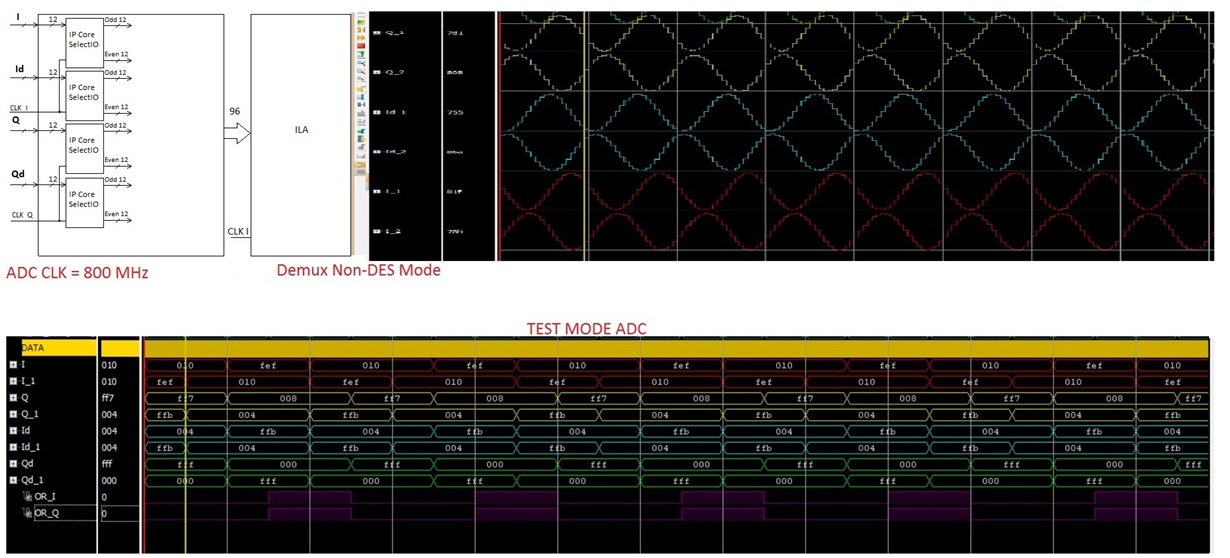

ADC 接收的时钟频率为800MHz。 ADC 多路信号分离器非 DES 模式。

CAL_ADC = 0

DDRPH_ADC = 0

ECE_ADC = 0

CALFLY_ADC = 0

FSR_ADC = 0

nDM_ADC = 0

TPM_ADC = 0

PDI_ADC = 0

PDQ_ADC = 0

DES_ADC = 0

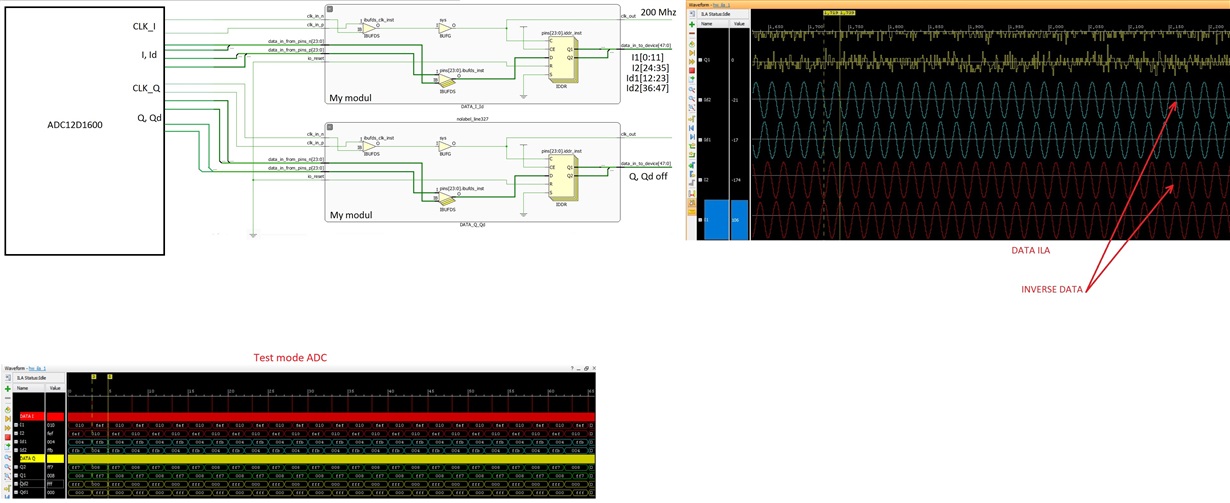

配置寄存器0x2010。 CLK_I 和 CLK_Q 200MHz。 数据被发送到 selectio。 我连接到 selectio ILA 的输出。 我将奇数数据反转。 ADC 测试模式数据正确。