请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADS5404 您好!

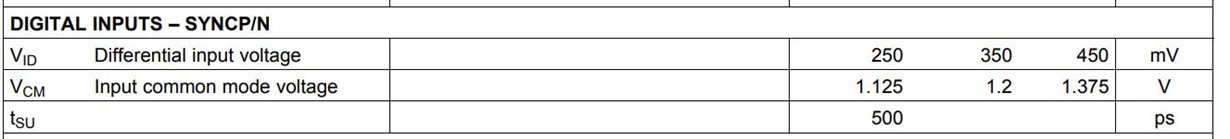

SYNC 引脚电压范围如下所示。

尽管我的客户从 FPGA 发送 SYNC 信号、但电压范围与以下条件不匹配;

FPGA LVDS 规格(1) Vodiff:247mV (最小值)、350mV (典型值)、600mV (最大值)

FPGA LVDS 规范(2)声码:1.0V (最小值)、1.25V (典型值)、1.425V (最大值)

我已经在寻找 TI 的 LVDS 缓冲器、但我无法找到满足上述输入规格的产品。

您有什么想法来解决它吗?

此致、

Kuramochi