主题中讨论的其他器件:DAC37J82、 LMK04828

大家好、我正在尝试在 DAC37J82和 FPGA 中的发送器之间建立链接

设置详细信息:

- DAC37J82EVM 电路板

- Xilinx VCU118演示板

- JESD204 v7.2.1 IP 被实例化

- JESD204B 子类1

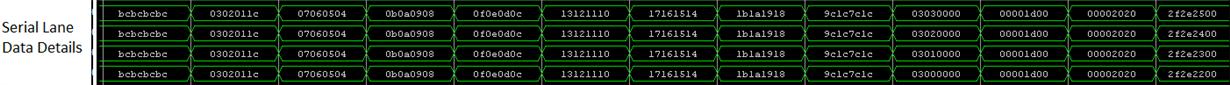

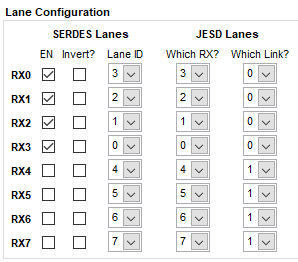

- LMFKS = 4、2、1、30、1

- 1GSPS 采样率、250MHz 内核时钟、10Gbps 线路速率

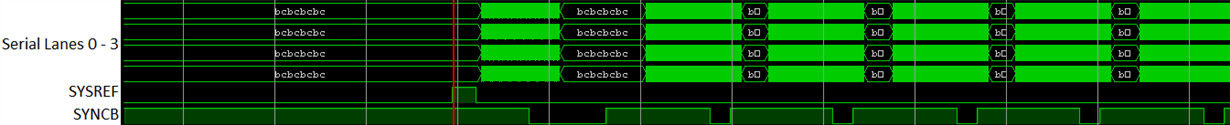

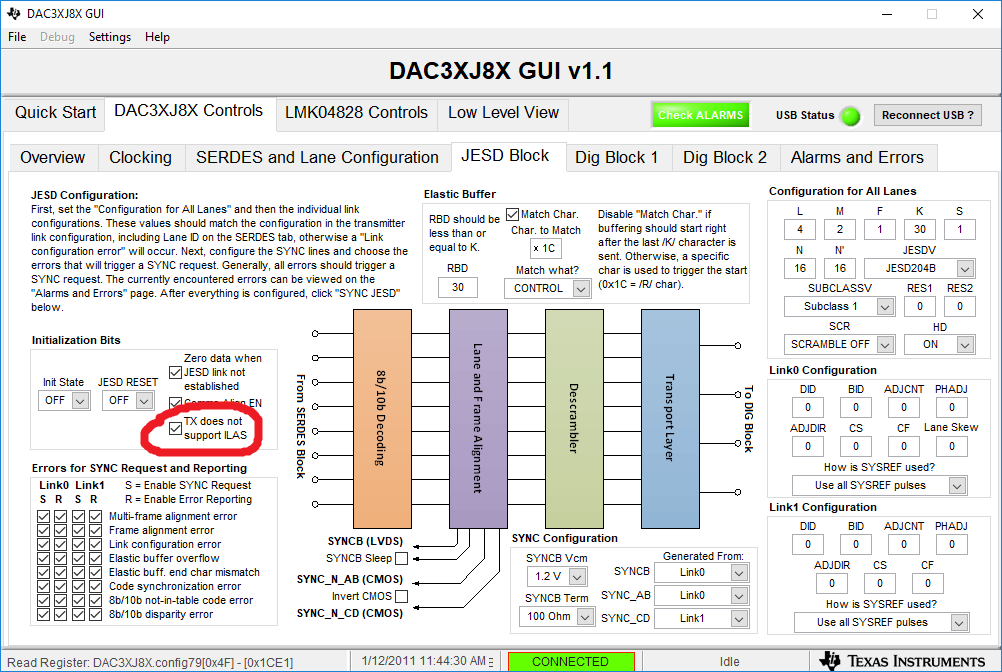

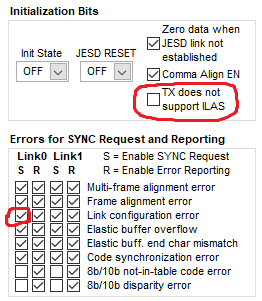

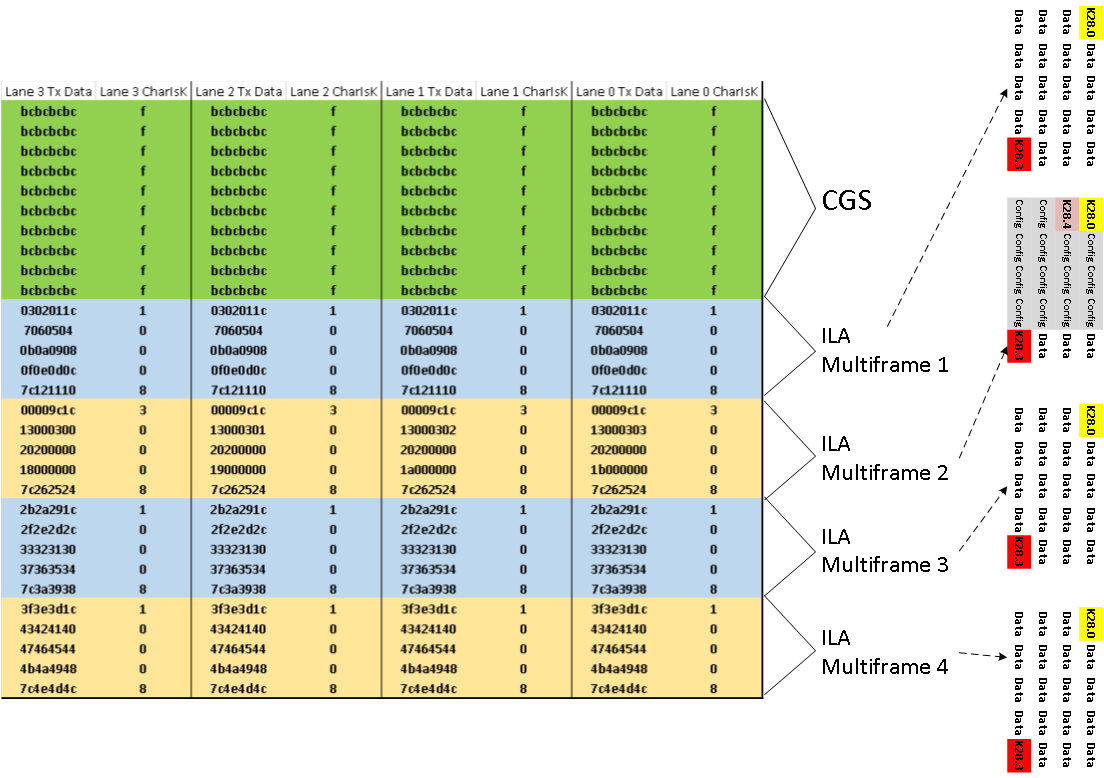

我已经按照 DAC37J82数据表第107页上的设置步骤操作、当我从 DAC EVM 上的 LMK04828触发 SYSREF 时、我看到 DAC 中的 SYNCB 线路在置为有效和置为无效之间无限期切换。 我不是很确定原因、因为 FPGA 输出的 ILA 序列看起来很好、只要我知道、在这种状态下、DAC EVM GUI 会报告通道0 - 3的通道配置错误。

如果我选中 DAC EVM GUI 中的"Tx 不支持 ILAS"复选框、看起来效果会更好。 我可以在频谱分析仪上验证我在 FPGA 中生成的374MHz 测试音是否被 DAC 正确输出。

如果您能帮助您了解 ILA 序列为何会中断 JESD 链路的建立、我们将不胜感激。